THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# **Efficient and Flexible Embedded Systems** and Datapath Components

Magnus Själander

Division of Computer Engineering

Department of Computer Science and Engineering

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden 2008

## Efficient and Flexible Embedded Systems and Datapath Components

Magnus Själander ISBN 978-91-7385-137-4

Copyright © Magnus Själander, 2008.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie 2818 ISSN 0346-718X

Technical report 40D

Department of Computer Science and Engineering

VLSI Research Group

Department of Computer Science and Engineering Chalmers University of Technology SE-412 96 Göteborg, Sweden Phone: +46 (0)31-772 10 00

Author e-mail: magnus@sjalander.com

### Cover:

Picture by the author. Illustration of a multi-core architecture with several Flex-Cores, where each core has a twin-precision multiplier.

Printed by Chalmers Reproservice Göteborg, Sweden 2008

# Efficient and Flexible Embedded Systems and Datapath Components

Magnus Själander

Division of Computer Engineering, Chalmers University of Technology

### ABSTRACT

The comfort of our daily lives has come to rely on a vast number of embedded systems, such as mobile phones, anti-spin systems for cars, and high-definition video. To improve the end-user experience at often stringent requirements, in terms of high performance, low power dissipation, and low cost, makes these systems complex and nontrivial to design.

This thesis addresses design challenges in three different areas of embedded systems. The presented FlexCore processor intends to improve the programmability of heterogeneous embedded systems while maintaining the performance of application-specific accelerators. This is achieved by integrating accelerators into the datapath of a general-purpose processor in combination with a wide control word consisting of all control signals in a FlexCore's datapath. Furthermore, a FlexCore processor utilizes a flexible interconnect, which together with the expressiveness of the wide control word improves its performance.

When designing new embedded systems it is important to have efficient components to build from. Arithmetic circuits are especially important, since they are extensively used in all applications. In particular, integer multipliers present big design challenges. The proposed twin-precision technique makes it possible to improve both throughput and power of conventional integer multipliers, when computing narrow-width multiplications. The thesis also shows that the Baugh-Wooley algorithm is more suitable for hardware implementations of signed integer multipliers than the commonly used modified-Booth algorithm.

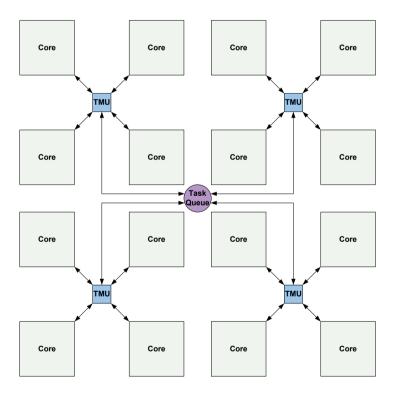

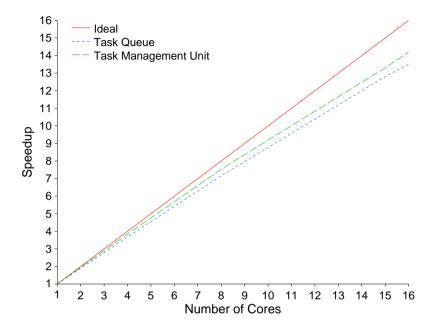

A multi-core architecture is a common design choice when a single-core architecture cannot deliver sufficient performance. However, multi-core architectures introduce their own design challenges, such as scheduling applications onto several cores. This thesis presents a novel task management unit, which offloads task scheduling from the conventional cores of a multi-core system, thus improving both performance and power efficiency of the system.

This thesis proposes novel solutions to a number of relevant issues that need to be addressed when designing embedded systems.

Keywords: Embedded, Flexible, Multi-Core, Multiplier, Scheduling, Twin-Precision

# List of Appended Papers

- A Martin Thuresson, Magnus Själander, Magnus Björk, Lars Svensson, Per Larsson-Edefors, and Per Stenström, "FlexCore: Utilizing Exposed Datapath Control for Efficient Computing," Accepted March 4, 2008, for publication in *Springer Journal of Signal Processing Systems*.

- **B Magnus Själander**, Per Larsson-Edefors and Magnus Björk, "A Flexible Datapath Interconnect for Embedded Applications," in *Proceedings of the 2007 IEEE Computer Society Annual Symposium on VLSI*, Porto Alegre, Brazil, May 9-11, 2007, pp. 15-20.

- C Magnus Själander and Per Larsson-Edefors, "The Case for HPM-Based Baugh-Wooley Multipliers," in *Department of Computer Science and En*gineering, Chalmers University of Technology, Technical Report 2008-8, Sweden, March 4, 2008.

- **D Magnus Själander**, Henrik Eriksson, and Per Larsson-Edefors, "An Efficient Twin-Precision Multiplier" in *Proceedings of the 2004 IEEE International Conference on Computer Design*, San Jose, California, USA, October 10-13, 2004, pp. 30-33.

- E Magnus Själander, Mindaugas Draždžiulis, Per Larsson-Edefors, and Henrik Eriksson, "A Low-Leakage Twin-Precision Multiplier Using Reconfigurable Power Gating" in *Proceedings of the 2005 IEEE International Symposium on Circuits and Systems*, Kobe, Japan, May 23-26, 2005, pp. 1654-1657.

- **F Magnus Själander** and Per Larsson-Edefors, "Multiplication Acceleration Through Twin Precision" Conditionally Accepted: Minor Revision, March 17, 2008, in *IEEE Transactions on VLSI Systems*.

- **G Magnus Själander**, Andrei Terechko, and Marc Duranton, "A Look-Ahead Task Management Unit for Embedded Multi-Core Architectures," Accepted for publication in *Proceedings of the 2008 Euromicro Conference on Digital System Design: Architectures, Methods and Tools*, Parma, Italy, September 3-5, 2008.

### Related publications that are not included in this thesis:

- Magnus Själander and Per Larsson-Edefors, "High-Speed and Low-Power Multipliers Using the Baugh-Wooley Algorithm and HPM Reduction Tree" Accepted for publication in *Proceedings of the 2008 IEEE International Conference on Electronics, Circuits, and Systems*, St. Julian's, Malta, August 31 September 3, 2008.

- ▶ Mafijul Md. Islam, Magnus Själander, and Per Stenström, "Early Detection and Bypassing of Trivial Operations to Improve Energy Efficiency of Processors" in *Elsevier Journal on Microprocessors and Microsystems*, 2008, doi:10.1016/j.micpro.2007.10.001.

- ▶ Martin Thuresson, Magnus Själander, Magnus Björk, Lars Svensson, Per Larsson-Edefors, and Per Stenström, "FlexCore: Utilizing Exposed Datapath Control for Efficient Computing" in *International Symposium* on Systems, Architectures, Modeling, and Simulation, Samos, Greece, July 16-19 2007, pp.18-25.

- ▶ Magnus Björk, Magnus Själander, Lars Svensson, Martin Thuresson, John Hughes, Kjell Jeppson, Jonas Karlsson, Per Larsson-Edefors, Mary Sheeran, and Per Stenström, "Exposed Datapath for Efficient Computing" in *HiPEAC Workshop on Reconfigurable Computing*, Ghent, Belgium, January 28-30 2006.

⊳ Henrik Eriksson, Per Larsson-Edefors, Mary Sheeran, Magnus Själander, Daniel Johansson, and Martin Schölin, "Multiplier Reduction Tree with Logarithmic Logic Depth and Regular Connectivity" in *Proceedings of the 2006 IEEE International Symposium on Circuits and Systems*, Kos, Greece, May 21-24, 2006, pp. 5-8.

### **Related Patent:**

▶ On March 12, 2008, patent application EP08102525 was filed at the European Patent Office for mechanisms in **Paper G**.

# Acknowledgments

I am grateful to the following people for what they have done for me, for my career, and for this thesis.

- ▶ Professor Per Larsson-Edefors† for believing in me and giving me the opportunity to pursue a research career.

- ► Martin Thuresson† for not only being a valued colleague and coauthor but also a good friend that have made the time at Chalmers both inter-esting and fun.

- ▶ Mafijul Islam for our fruitful collaboration on how to bypass trivial operations.

- Daniel Andersson, Daniel Eckerbert, Minh Quang Do, and Tung Hoang as part of the VLSI research group and creating an interesting and inspiring working environment.

- ▶ Jim Nilsson for our early brainstorm on reconfigurable multipliers.

- ▶ Lars 'J' Svensson<sup>†</sup> for our combined struggles in the FlexSoC project.

- ► Magnus Björk, Thomas Schilling, Jonas Ferry, Erik Ryman, Jan Mårts, and Tomas Carlqvist for their efforts in the FlexSoC project.

- lander, Pierre Kleberger, Lars Kollberg, and Ulf Larsson for creating a good working environment.

- Marc Duranton for accepting me as an intern at NXP Semiconductors and Andrei Terechko for his guidance and many interesting discussions regarding multi-core architectures.

- ▶ Per Stenström and the HiPEAC European Network of Excellence for helping me fund my stay at NXP Semiconductors.

- ➤ The Swedish Foundation for Strategic Research (SSF) for their funding of my position at Chalmers University of Technology.

- Sten Gunnarsson† and Wolfgang John† for many great times while hiking in the woods, climbing in and around Göteborg, ice-skating on some lake that barely has ice, or kayaking in the archipelago.

- ➤ Tom Ashby, Loïc Baggetto, Ana Bosque Arbiol, Marius Grannæs, Robert Juenemann and Alberto, who I have had the great pleasure to get to know during my time as a Ph.D student and spent many great times with, in Göteborg and other exotic places.

- ▶ Jessica Leong for encouraging me to become a Ph.D student.

- My beloved grandmother Sonja Kallin for always supporting me and making it possible to start my academic career by letting me stay at her house when I had evening classes at the Mid Sweden University.

- ▶ My Uncle Harald Kallin for inspiring me to become an engineer.

- ▶ My parents Thomas and Ingeborg and my brother Lars for always supporting and encouraging me to pursue new challenges in life.

- ▶ Madelene Egardt for all her love and support. I love you.

A special thanks goes to all the people marked with the †-symbol who have read and given valuable comments on this thesis.

Magnus Själander Göteborg, June 2008

# Contents

| Al | ostrac  | t                                                       |                                            | i    |  |  |  |  |  |  |  |

|----|---------|---------------------------------------------------------|--------------------------------------------|------|--|--|--|--|--|--|--|

| Li | st of A | Appende                                                 | ed Papers                                  | iii  |  |  |  |  |  |  |  |

| A  | cknow   | ledgme                                                  | nts                                        | vii  |  |  |  |  |  |  |  |

| 1  | Intr    | oductio                                                 | n                                          | 1    |  |  |  |  |  |  |  |

|    | 1.1     | FlexCo                                                  | ore                                        | . 4  |  |  |  |  |  |  |  |

|    | 1.2     | Multip                                                  | lier Implementations                       | . 8  |  |  |  |  |  |  |  |

|    |         | 1.2.1                                                   | Single-Precision Multiplier                | . 8  |  |  |  |  |  |  |  |

|    |         | 1.2.2                                                   | Twin-Precision Multiplier                  | . 12 |  |  |  |  |  |  |  |

|    | 1.3     | Task S                                                  | cheduling for Multi-Core Architectures     | . 15 |  |  |  |  |  |  |  |

|    | 1.4     | Conclu                                                  | asion                                      | . 17 |  |  |  |  |  |  |  |

|    | Bibli   | iography                                                | y                                          | . 18 |  |  |  |  |  |  |  |

| A  | Utili   | lizing Exposed Datapath Control for Efficient Computing |                                            |      |  |  |  |  |  |  |  |

|    | A.1     | Introdu                                                 | action                                     | . 26 |  |  |  |  |  |  |  |

|    | A.2     | The Ba                                                  | aseline FlexCore Architecture              | . 28 |  |  |  |  |  |  |  |

|    |         | A.2.1                                                   | N-ISA: Exposed Datapath                    | . 30 |  |  |  |  |  |  |  |

|    | A.3     | Extens                                                  | ions to the Baseline FlexCore              | . 31 |  |  |  |  |  |  |  |

|    |         | A.3.1                                                   | Multiplier Extension                       | . 32 |  |  |  |  |  |  |  |

|    | A.4     | Compi                                                   | ling for FlexCore                          | . 32 |  |  |  |  |  |  |  |

|    |         | A.4.1                                                   | Instruction-Level Static Code Optimization | . 34 |  |  |  |  |  |  |  |

|    |         | A.4.2                                                   | Scheduling Opportunities                   | . 35 |  |  |  |  |  |  |  |

|    | A.5     | Experi                                                  | mental Framework                           | . 38 |  |  |  |  |  |  |  |

|    |         |                                                         |                                            |      |  |  |  |  |  |  |  |

x CONTENTS

|   |             | A.5.1 Hardware Implementation                             | 9 |

|---|-------------|-----------------------------------------------------------|---|

|   | A.6         | Results                                                   | 2 |

|   |             | A.6.1 Cycle-Count Evaluation                              | 2 |

|   |             | A.6.2 Performance Evaluation                              | 4 |

|   |             | A.6.3 Static Code Size                                    | 0 |

|   | A.7         | Related Work                                              | 1 |

|   | A.8         | Conclusion                                                | 3 |

|   | Bibli       | ography                                                   | 4 |

| В | A FL        | exible Datapath Interconnect for Embedded Applications 59 | o |

| J | B.1         | Introduction                                              |   |

|   | B.2         | Architectural Framework                                   |   |

|   | <b>D</b> .2 | B.2.1 Modeling of the Architectures                       |   |

|   | B.3         | Experimental Framework                                    |   |

|   | <b>D</b> .5 | B.3.1 Compiler                                            |   |

|   |             | B.3.2 Cycle-Accurate Simulator                            |   |

|   |             | B.3.3 HDL Generator                                       |   |

|   | B.4         | Interconnect Evaluation                                   |   |

|   |             | B.4.1 FFT Application Scheduling 6                        | 7 |

|   |             | B.4.2 Hardware Implementation                             | 8 |

|   | B.5         | Results                                                   | 0 |

|   | B.6         | Discussion                                                | 3 |

|   | B.7         | Conclusion                                                | 7 |

|   | B.8         | Acknowledgments                                           | 8 |

|   | Bibli       | ography                                                   | 8 |

| C | The         | Case for HPM-Based Baugh-Wooley Multipliers 83            | 3 |

| C | C.1         | Introduction                                              |   |

|   | C.2         | Modified-Booth Multiplication                             |   |

|   | C.2         | C.2.1 Modified-Booth Implementation                       |   |

|   | C.3         | Baugh-Wooley Multiplication                               |   |

|   | C.3         | C.3.1 Baugh-Wooley Implementation                         |   |

|   | C.4         | An Initial Gate-Level Study                               |   |

|   | C.5         | Multiplier Evaluation Setup                               |   |

|   |             |                                                           |   |

*CONTENTS* xi

|   | C.6   | Modified-Booth Multiplier Evaluation                      |

|---|-------|-----------------------------------------------------------|

|   |       | C.6.1 Yeh Recoding                                        |

|   |       | C.6.2 Hsu Recoding                                        |

|   |       | C.6.3 Recoding Scheme Comparison                          |

|   | C.7   | Baugh-Wooley Multiplier Evaluation                        |

|   | C.8   | Comparison of Baugh-Wooley and Modified-Booth 98          |

|   |       | C.8.1 Dissecting the Timing                               |

|   | C.9   | Implementation Aspects of the Reduction Tree              |

|   | C.10  | Implementation in a 65-nm Process Technology 104          |

|   | C.11  | Partial-Product Generation and Final Adders               |

|   | C.12  | Conclusion                                                |

|   | Bibli | ography                                                   |

| D | An I  | Efficient Twin-Precision Multiplier 111                   |

|   | D.1   | Introduction                                              |

|   | D.2   | Design Exploration                                        |

|   |       | D.2.1 Tree Multiplier                                     |

|   |       | D.2.2 Signed Multiplication According to Baugh-Wooley 115 |

|   | D.3   | Final Adder                                               |

|   | D.4   | Simulation Setup and Results                              |

|   | D.5   | Conclusion                                                |

|   | Bibli | ography                                                   |

| E | A Lo  | ow-Leakage Twin-Precision Multiplier 125                  |

|   | E.1   | Introduction                                              |

|   | E.2   | Preliminaries                                             |

|   |       | E.2.1 The Twin-Precision Multiplier                       |

|   |       | E.2.2 Circuits for Leakage Reduction                      |

|   | E.3   | Power Supply Grid and Tree Organization                   |

|   | E.4   | Simulation and Results                                    |

|   | E.5   | Conclusions                                               |

|   | Bibli | ography                                                   |

xii CONTENTS

| F | Mult  | tiplicati                           | ion Acceleration Through Twin Precision             | 139   |  |  |  |  |  |  |  |  |

|---|-------|-------------------------------------|-----------------------------------------------------|-------|--|--|--|--|--|--|--|--|

|   | F.1   | 1 Introduction                      |                                                     |       |  |  |  |  |  |  |  |  |

|   | F.2   | Twin-I                              | Precision Fundamentals                              | . 142 |  |  |  |  |  |  |  |  |

|   |       | F.2.1                               | A First Implementation                              | . 146 |  |  |  |  |  |  |  |  |

|   |       | F.2.2                               | An HPM Implementation                               | . 148 |  |  |  |  |  |  |  |  |

|   |       | F.2.3                               | The Final Adder                                     | . 148 |  |  |  |  |  |  |  |  |

|   | F.3   | A Bau                               | gh-Wooley Implementation                            | . 149 |  |  |  |  |  |  |  |  |

|   |       | F.3.1                               | Algorithms for Baugh-Wooley                         | . 149 |  |  |  |  |  |  |  |  |

|   |       | F.3.2                               | Twin-Precision Using the Baugh-Wooley Algorithm     | . 149 |  |  |  |  |  |  |  |  |

|   | F.4   | F.4 A Modified-Booth Implementation |                                                     |       |  |  |  |  |  |  |  |  |

|   |       | F.4.1                               | Algorithms for Modified Booth                       | . 153 |  |  |  |  |  |  |  |  |

|   |       | F.4.2                               | Twin-Precision Using the modified-Booth Algorithm . | . 154 |  |  |  |  |  |  |  |  |

|   | F.5   | Netlist                             | Generation and Evaluation Setup                     | . 158 |  |  |  |  |  |  |  |  |

|   |       | F.5.1                               | Synthesis and Layout of Baugh-Wooley Netlists       | . 159 |  |  |  |  |  |  |  |  |

|   |       | F.5.2                               | Synthesis and Layout of Modified-Booth Netlists     | . 160 |  |  |  |  |  |  |  |  |

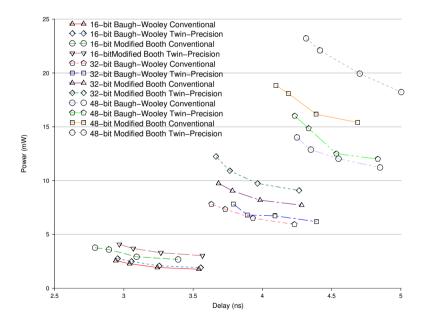

|   | F.6   | Result                              | s and Discussion                                    | . 161 |  |  |  |  |  |  |  |  |

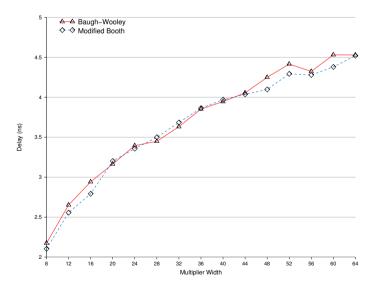

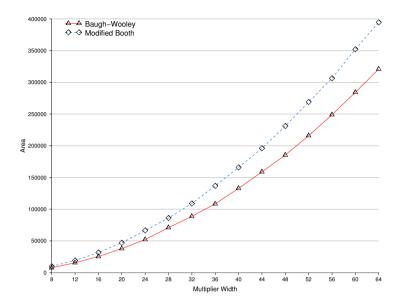

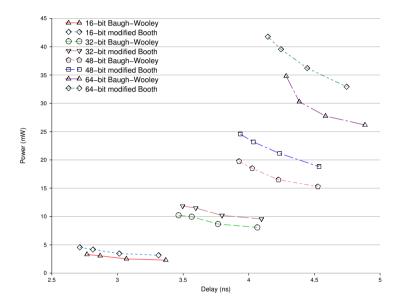

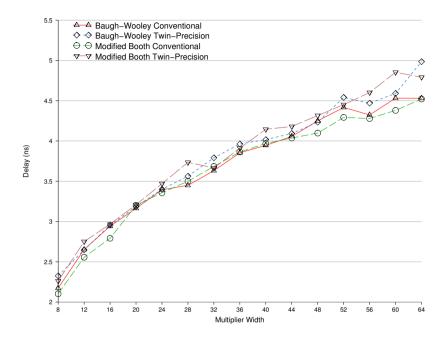

|   |       | F.6.1                               | Delay                                               | . 162 |  |  |  |  |  |  |  |  |

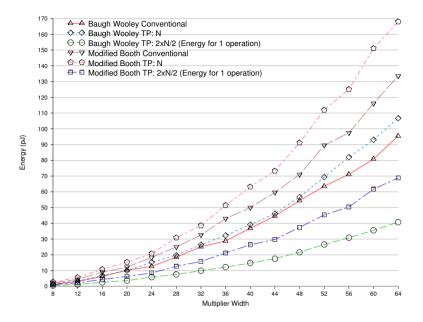

|   |       | F.6.2                               | Energy per Operation                                | . 162 |  |  |  |  |  |  |  |  |

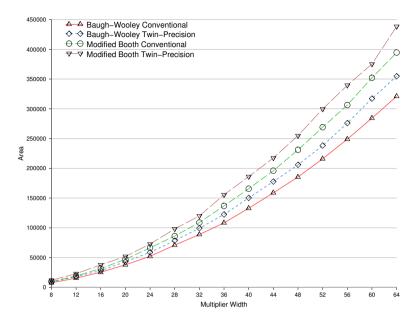

|   |       | F.6.3                               | Area                                                | . 164 |  |  |  |  |  |  |  |  |

|   |       | F.6.4                               | Power Reduction by the Use of Power Gating          | . 164 |  |  |  |  |  |  |  |  |

|   | F.7   | Implementation in a 65-nm Process   |                                                     |       |  |  |  |  |  |  |  |  |

|   | F.8   | Workload Characterization           |                                                     |       |  |  |  |  |  |  |  |  |

|   | F.9   | SIMD                                | Multiplier Extension, a Case Study                  | . 172 |  |  |  |  |  |  |  |  |

|   |       | F.9.1                               | Instruction Set Extension                           | . 172 |  |  |  |  |  |  |  |  |

|   |       | F.9.2                               | Arithmetic Logic Unit                               | . 174 |  |  |  |  |  |  |  |  |

|   |       | F.9.3                               | Evaluation and Results                              | . 175 |  |  |  |  |  |  |  |  |

|   | F.10  | 10 Conclusions                      |                                                     |       |  |  |  |  |  |  |  |  |

|   | F.11  | 1 Acknowledgment                    |                                                     |       |  |  |  |  |  |  |  |  |

|   | Bibli | ograph                              | y                                                   | . 179 |  |  |  |  |  |  |  |  |

| G | A Lo  | A Look-Ahead Task Management Unit   |                                                     |       |  |  |  |  |  |  |  |  |

|   | G.1   | 1 Introduction                      |                                                     |       |  |  |  |  |  |  |  |  |

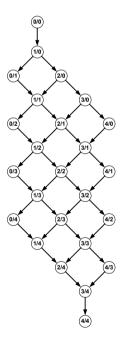

|   | G.2   | Paralle                             | el Applications with Task Dependencies              | . 188 |  |  |  |  |  |  |  |  |

|   |       | G.2.1                               | H.264 Video Decoder                                 | . 188 |  |  |  |  |  |  |  |  |

| G.4       Task Management Unit       194         G.4.1       Look-Ahead Task Management       196         G.5       Evaluation Setup       198         G.5.1       TriMedia H.264 Video Decoder       199         G.5.2       H.264 on the Reference Architecture       199         G.5.3       H.264 on the TMU Architecture       201         G.6       Results       202         G.7       Related Work       204         G.8       Future Work       204         G.9       Conclusions       205         G.10       Acknowledgments       205         Bibliography       205 | G.3   | Task M  | anage  | men  | ıt. |     |            |     |     |     |      |    |     |    |  |  |  | . 191 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|--------|------|-----|-----|------------|-----|-----|-----|------|----|-----|----|--|--|--|-------|

| G.5       Evaluation Setup       198         G.5.1       TriMedia H.264 Video Decoder       199         G.5.2       H.264 on the Reference Architecture       199         G.5.3       H.264 on the TMU Architecture       201         G.6       Results       202         G.7       Related Work       204         G.8       Future Work       204         G.9       Conclusions       205         G.10       Acknowledgments       205                                                                                                                                          |       |         | _      |      |     |     |            |     |     |     |      |    |     |    |  |  |  |       |

| G.5.1       TriMedia H.264 Video Decoder       199         G.5.2       H.264 on the Reference Architecture       199         G.5.3       H.264 on the TMU Architecture       201         G.6       Results       202         G.7       Related Work       204         G.8       Future Work       204         G.9       Conclusions       205         G.10       Acknowledgments       205                                                                                                                                                                                       |       | G.4.1   | Look   | -Ah  | ead | Tas | k N        | Лaı | nag | en  | nen  | t  |     |    |  |  |  | . 196 |

| G.5.2       H.264 on the Reference Architecture       199         G.5.3       H.264 on the TMU Architecture       201         G.6       Results       202         G.7       Related Work       204         G.8       Future Work       204         G.9       Conclusions       205         G.10       Acknowledgments       205                                                                                                                                                                                                                                                  | G.5   | Evaluat | ion Se | etup |     |     |            |     |     |     |      |    |     |    |  |  |  | . 198 |

| G.5.3       H.264 on the TMU Architecture       201         G.6       Results       202         G.7       Related Work       204         G.8       Future Work       204         G.9       Conclusions       205         G.10       Acknowledgments       205                                                                                                                                                                                                                                                                                                                    |       | G.5.1   | TriM   | edia | H.2 | 264 | Vi         | dec | D   | eco | ode  | r  |     |    |  |  |  | . 199 |

| G.6 Results       202         G.7 Related Work       204         G.8 Future Work       204         G.9 Conclusions       205         G.10 Acknowledgments       205                                                                                                                                                                                                                                                                                                                                                                                                              |       | G.5.2   | H.26   | 4 on | the | Re  | fer        | enc | e A | ١rc | hit  | ec | tuı | e. |  |  |  | . 199 |

| G.7 Related Work       204         G.8 Future Work       204         G.9 Conclusions       205         G.10 Acknowledgments       205                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | G.5.3   | H.264  | 4 on | the | TN  | <b>1</b> U | Ar  | chi | tec | etui | re |     |    |  |  |  | . 201 |

| G.8 Future Work       204         G.9 Conclusions       205         G.10 Acknowledgments       205                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | G.6   | Results |        |      |     |     |            |     |     |     |      |    |     |    |  |  |  | . 202 |

| G.9 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | G.7   | Related | Work   | Ξ.   |     |     |            |     |     |     |      |    |     |    |  |  |  | . 204 |

| G.10 Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | G.8   | Future  | Work   |      |     |     |            |     |     |     |      |    |     |    |  |  |  | . 204 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | G.9   | Conclu  | sions  |      |     |     |            |     |     |     |      |    |     |    |  |  |  | . 205 |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | G.10  | Acknow  | vledgi | nent | ts  |     |            |     |     |     |      |    |     |    |  |  |  | . 205 |

| 0 1 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bibli | ography |        |      |     |     |            |     |     |     |      |    |     |    |  |  |  | . 205 |

xiv CONTENTS

# Introduction

Our modern lifestyle depends on a wide range of functionalities that are provided by numerous embedded systems, such as the fuel injection system of combustion engines, home entertainment systems, and mobile devices. Moreover, there is a general trend towards increasing numbers of embedded systems in our daily lives and in order to meet customer demands, these systems tend to become increasingly more complex with each new generation.

The strive towards higher performance and more functionality in combination with stringent requirements makes general-purpose processors unsuitable for embedded systems. A high-end general-purpose processor tends to have excessively high power dissipation requirements, which would quickly drain the battery of a mobile device and would require costly parts for cooling. A common design practice used to achieve required performance at low power and small area is to design heterogeneous system-on-chips, where specialized hardware accelerators are controlled by one or more embedded microproces-

sors, such as an ARM core [1]. However, designing heterogeneous system-onchips, which are flexible and can cater for new applications that are not within the original set of targeted applications, is difficult and require great engineering efforts. Application Specific Instruction-set Processors (ASIPs), such as Tensillica's Xtensa family [2], try to combine the performance benefits from heterogeneous system-on-chips with the flexibility of general-purpose processors. An ASIP is generally based on a small general-purpose processor with a limited instruction set, to which application-specific instructions are added. Instructions can be added by combining several conventional instructions into one new instruction, so called instruction-fusion, or by adding specialized hardware accelerators to the datapath of the processor. By introducing accelerators into the instruction set of the processor a homogeneous interface to the hardware is created. This allows for the use of a conventional software tool-flow, where specific hardware accelerators can be accessed through assembler instructions or by software macros in high-level languages. However, a disadvantage with an adaptable instruction set is that applications might not be binary compatible between different architectural implementations and need to be recompiled.

This thesis presents the FlexCore processor, which is based on the ideas of the FlexSoC [3] approach on how to build embedded systems. The Flex-Core processor combines the flexibility of general-purpose processors with the performance of specialized hardware accelerator units. This is achieved by integrating hardware accelerators into the datapath of a general-purpose processor. In contrast to conventional processors and ASIPs, a FlexCore processor does not have a conventional instruction set, where an instruction controls a set of pipeline stages over several clock cycles. A FlexCore processor instead has a wide control word that controls the whole datapath for a single clock cycle. The wide control word consists of all control signals to all units and the interconnect in the FlexCore datapath. A datapath unit can in this case be anything from a register to some specialized hardware accelerator. Moving away from a conventional instruction set to an architecture with a wide control word, which is exposed to the compiler/programmer, gives an application detailed control of the hardware. The increased controllability has earlier been shown to improve a datapath's performance [4, 5].

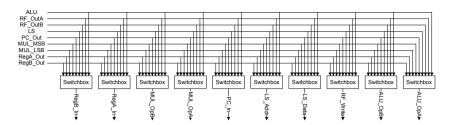

The interconnect of a FlexCore processor is, in the early stage of the processor development, a fully connected crossbar switch that connects the different datapath units. The flexible interconnect together with an easily extendable control word make it extremely easy to add new datapath units to a FlexCore processor. The required input and output ports are added to the interconnect and the control word is appended with control signals for the new datapath unit and for addressing the new ports of the interconnect. However, a fully connected crossbar does not scale well. Therefore, once a set of datapath units has been chosen, the compiler together with the intended set of applications can be used to eliminate superfluous paths from the interconnect.

The wide control word would be an unsuitable format for storing applications, because of the large memory space it would require. The FlexSoC approach therefore envisions a dynamically reconfigurable instruction decoder that allows for a more compact representation of the control word. The reconfigurable instruction decoder makes it possible to tailor an instruction set for a specific application or set of applications. However, the reconfigurable instruction decoder is not within the scope of this thesis.

When designing digital systems, such as a FlexCore processor, it is important to have efficient datapath units to build the system from. One such datapath unit is the integer multiplier which is frequently used in typical embedded applications, such as signal processing and multimedia applications. Integer multiplier implementations tend to be both large in terms of area and have a high power dissipation, relative other arithmetic circuits. This thesis presents the twin-precision technique, which makes it possible for an integer multiplier to efficiently compute narrow-width multiplications (i.e. 16-bit multiplications on a 32-bit multiplier) and to increase the throughput by executing two narrow-width multiplications in parallel. Furthermore, an evaluation is presented where the modified-Booth algorithm [6] is compared to the Baugh-Wooley algorithm [7].

The increasing demand for performance leads to a point where single processors cannot, at least in a power efficient way, deliver required performance. At this point multi-core systems is the only promising solution. However, for a single application to take advantage of the available performance of a multi-core system it is necessary to schedule the application onto all cores of the system.

For this reason a task-management unit is proposed to accelerate and offload the scheduling overhead that is introduced when a multi-task application is distributed over a set of processor cores.

# 1.1 FlexCore

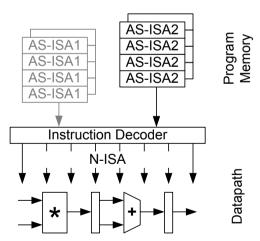

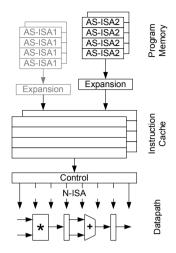

The FlexSoC [3] research project attempts to combine the performance and energy efficiency of hardware accelerators with the flexibility of programmable processors by introducing a uniform programming interface. This is achieved by moving away from conventional Instruction Set Architectures (ISAs). Instead, a two-tier ISA is defined, with a wide Native-ISA (N-ISA) capable of fine-grained control of all computational resources of a datapath and customizable Application Specific-ISAs (AS-ISAs) that can be made compact and thus suitable for storing applications in memory. A reconfigurable instruction decoder decodes AS-ISA instructions into N-ISA instructions. The instruction decoder is reconfigurable to allow for the creation of customized AS-ISAs for a particular application or set of applications. An illustration of the FlexSoC concept is shown in Fig. 1.1.

**Figure 1.1:** *Illustration of a FlexSoC system with AS-ISA to N-ISA decoding.*

1.1. FLEXCORE 5

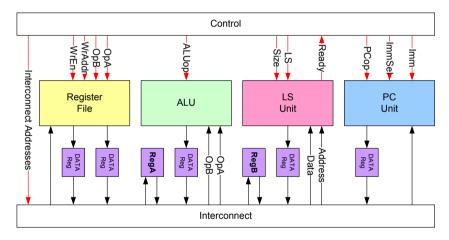

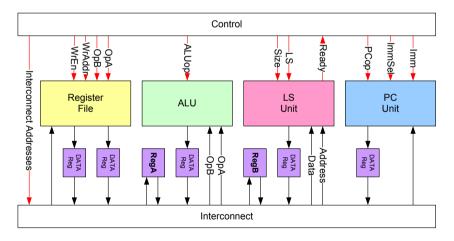

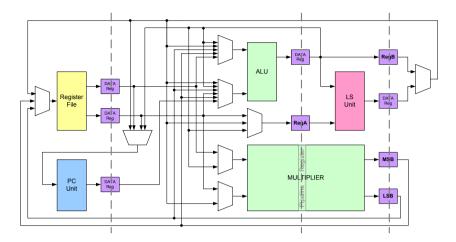

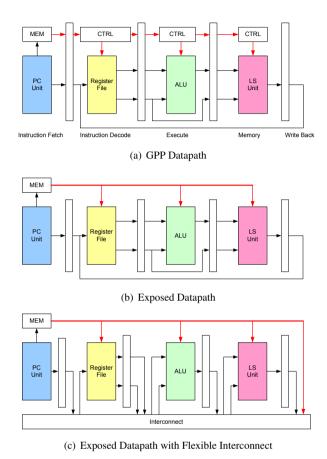

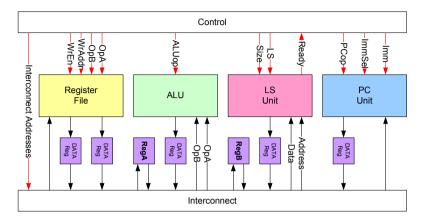

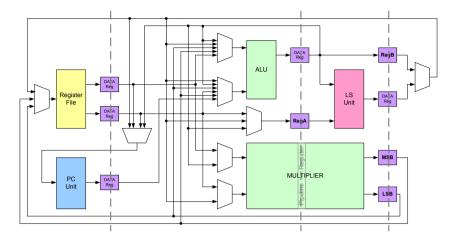

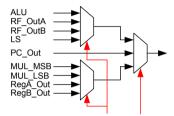

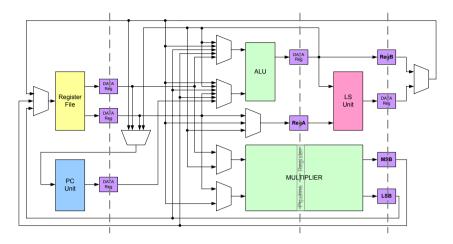

A new processor architecture, called FlexCore, has been designed to evaluate the idea of a two-tier ISA. A FlexCore processor, in its simplest form, consists of all the datapath units of a conventional single-issue five-stage pipeline, similar to the Hennessy-Patterson 32-bit DLX and MIPS R2000 [8]. Application-specific hardware accelerators can then be added as new datapath units for improved performance and energy efficiency. All datapath units are connected to a flexible interconnect that allows data to be freely routed between the different datapath units. The datapath units together with the interconnect make it possible for a FlexCore processor to emulate a five-stage pipeline of a General-Purpose Processor (GPP) and can therefore offer the full programmability of a GPP. The N-ISA is defined as the collection of all control signals of each datapath unit and the address signals of the interconnect. Fig. 1.2 shows an illustration of the baseline FlexCore processor without any added hardware accelerators, where the N-ISA is seen as all the signals leaving the control.

**Figure 1.2:** Illustration of a baseline FlexCore. Note that RegA and RegB are used as pipeline registers when the FlexCore operates as a five-stage GPP pipeline.

The N-ISA changes the abstraction level at which the programmer/compiler can control the datapath compared to a conventional ISA. The abstraction level of a conventional ISA is the register file, where the input-operand(s) of each instruction of a conventional ISA is assumed to be available. If an input-operand

is not yet available in the register file, the hardware either stalls the instruction or dynamically reroutes the result of a previous instruction, which has already been executed but not yet written its result to the register file. This abstraction simplifies scheduling of instructions, since it is not necessary to keep track of individual hardware resources in the datapath. However, it also limits the control of the datapath and creates unnecessary pressure on the register file, which can degrade performance. The extra pressure is created since all instructions write their result to the register file, even though in many cases the result of an instruction is temporal and consumed by the following executed instruction. In this case the result could be routed directly between the two consecutive instructions, without writing it to the register file.

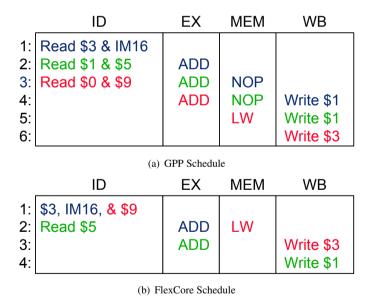

The abstraction of the N-ISA is at the datapath level, which gives the compiler/programmer full control of the whole datapath in each clock cycle. This complicates scheduling, since the operation of each individual datapath unit and routing of data between the units have to be scheduled for each cycle by the compiler/programmer. However, the increased controllability makes it possible to more freely schedule instructions and route data between datapath units. This improves both performance and reduces register file access, which can have a positive effect on the power dissipation. An example of how the N-ISA makes it possible to improve instruction scheduling can be found in **Paper A**, together with a more detailed description of the FlexCore processor.

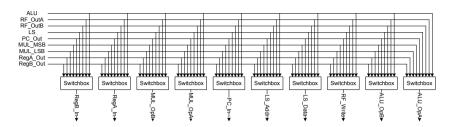

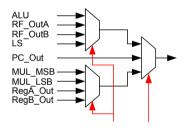

The FlexCore processor has a flexible interconnect, which is presented in **Paper B**. In the early stages of a FlexCore's development, the interconnect consists of a fully connected crossbar switch. The high connectivity between different datapath units allows for a more efficient scheduling, compared to more restricted interconnects, such as that of a GPP. The interconnect also makes it easy to add new datapath units to a FlexCore, since there never are any special cases, like forwarding paths, to cater for. A fully connected crossbar switch is costly to implement and does not scale well for reasonable large number of ports. However, a FlexCore processor is statically scheduled, which makes it possible to determine exactly the interconnect paths that will be used for a set of applications. The unused paths can then be removed without any impact on the performance in terms of executed cycles. By making sure that no paths associ-

1.1. FLEXCORE 7

ated with a conventional GPP interconnect is removed, the full programmability of a GPP can still be maintained.

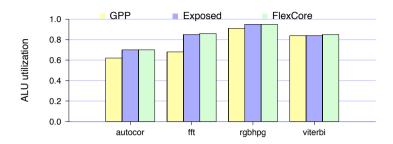

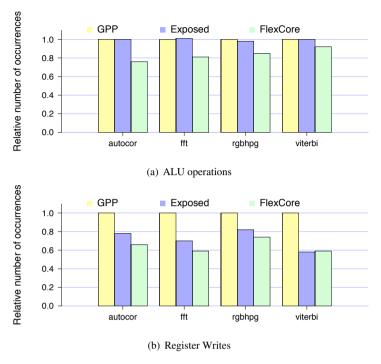

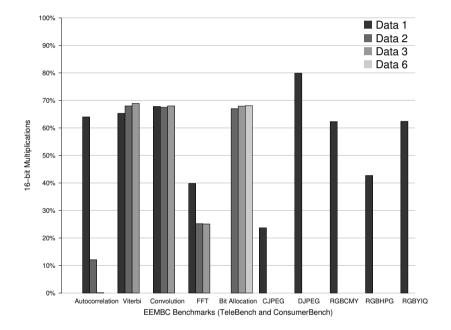

The wide control word and the fully connected interconnect are in **Paper A** shown to reduce the executed number of cycles with 10-36% for a set of four different applications from the EEMBC Telecom and Consumer benchmark suites [9]. It is also shown that 48% of all the paths in the fully-connected interconnect are never used by the executed set of applications. Further, in comparison to a FlexCore processor with the interconnect of a GPP in a 65 nm process technology, a tailored interconnect is shown to have negligible impact on performance and power of a FlexCore processor, with a reasonable increase of 6% in area. The same tailored interconnect improves the total execution time and energy dissipation of the four applications with 9-19% and 10-21%, respectively. Interesting to note is that for one of the applications (Viterbi) the execution time is not improved by the wide control word, while the tailored interconnect contributes to an improved performance for all four applications.

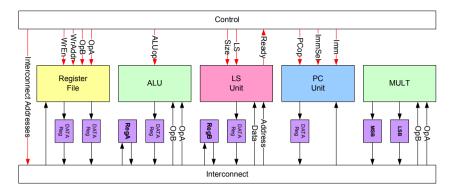

The FlexCore architecture has been designed to be easily extendable with new datapath units. An example of its extendibility is presented as a case study in **Paper F**. In the case study, a twin-precision multiplier is added to a FlexCore processor and new operations are added to its Arithmetic Logic Unit (ALU). The extended FlexCore is then used to emulate the execution of a GPP, instead of utilizing its full scheduling potential. The software tool-flow for the FlexCore architecture was therefore updated with five new assembler instructions and a Fast Fourier Transform (FFT) application was manually modified to take advantage of the new instructions. The result is a FlexCore processor with light-weight Single Instruction Multiple Data (SIMD) support that can be programmed at the assembler level. For the FFT application, this translates to 15% faster execution, compared to executing the FFT on a FlexCore with a conventional multiplier and no SIMD support.

The FlexCore processor has made it possible to evaluate the performance benefits that can be achieved by the expressive N-ISA. Furthermore, N-ISA instruction traces from executions of applications provide vital information for experimenting with the implementation of reconfigurable instruction decoders and the creation of customized AS-ISAs.

# 1.2 Multiplier Implementations

Multiplication is a common and important arithmetic operation in typical embedded applications, such as multimedia and digital signal processing. However, multiplier implementations tend to be larger, slower, and more power dissipating, compared to other arithmetic circuits. It is not uncommon that a multiplier unit is larger than the whole Arithmetic Logic Unit (ALU) of a processor. An efficient multiplier implementation can therefore have significant impact on the size and power of an embedded processor.

# 1.2.1 Single-Precision Multiplier

There are several possible ways of implementing multiplications. From the simplest being an implementation in software, where the multiplication is iterated over an adder and shifter, to hardware-implemented parallel multipliers. Parallel multipliers can be divided into three distinct steps. In the first step, a set of partial products is generated that are then fed to the second step, which is some type of a reduction circuit. The reduction circuit reduces the set of generated partial products into two bit vectors. In the third and final step, the two remaining bit vectors are summed together using a final adder.

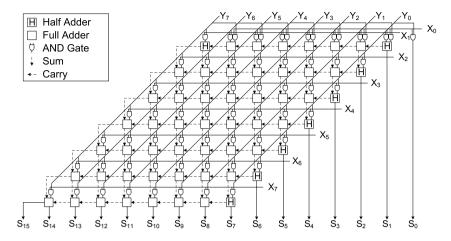

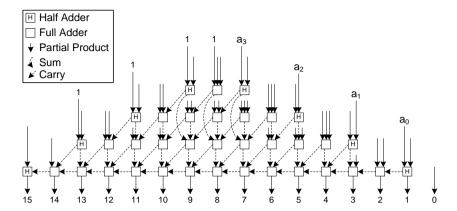

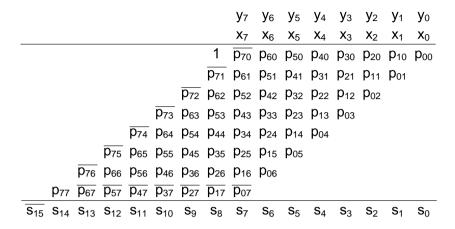

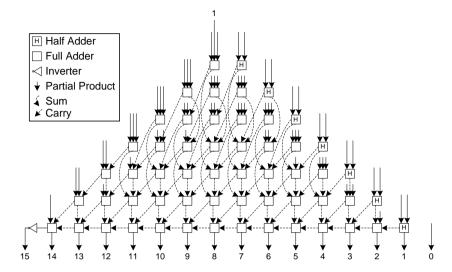

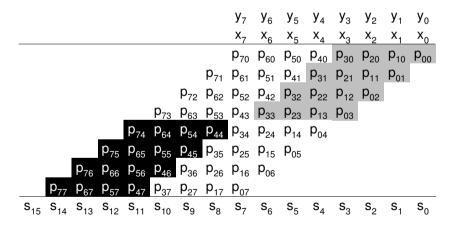

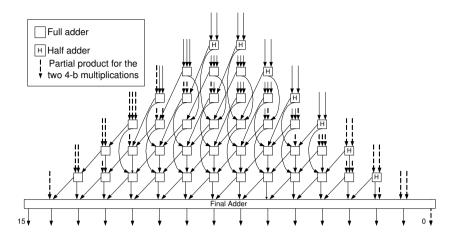

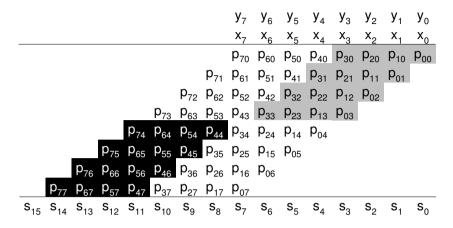

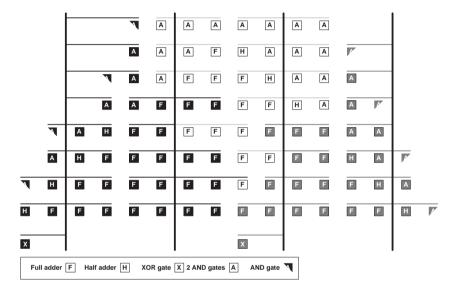

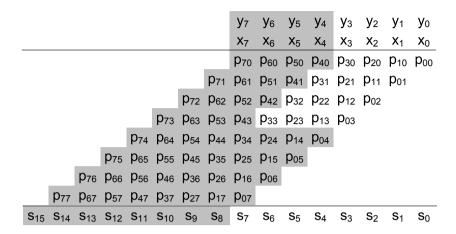

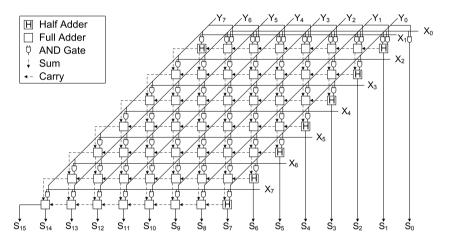

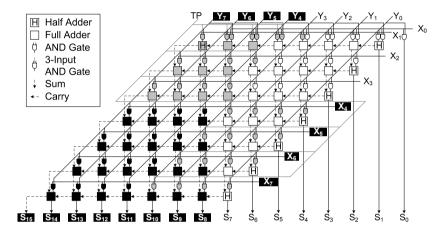

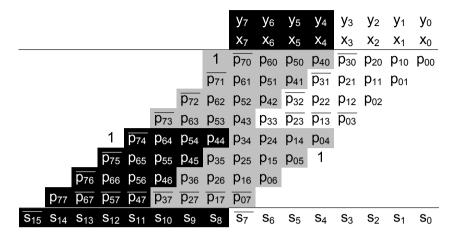

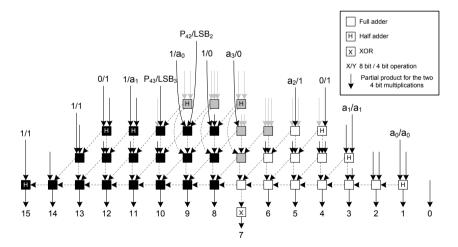

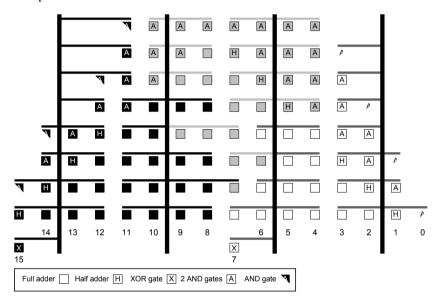

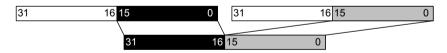

The first parallel multipliers, called array multipliers, were designed as an array of 3-input Full Adders (FAs) and utilized AND-gates to generate the partial products. Fig. 1.3 shows a block diagram of an unsigned 8-bit array multiplier, where the X multiplier-operand is multiplied with the Y multiplicand-operand in a  $X \times Y = S$  multiplication. For each bit in the multiplier-operand  $(x_0 \text{ to } x_7)$  a row of partial products is generated by connecting the bit of the multiplier-operand to the inputs of a row of 2-input AND-gates. The second input of each AND-gate is then connected to a bit of the multiplicand-operand  $(y_0 \text{ to } y_7)$ . The two first rows of partial products are then added together by a row of FAs. For each additional row of partial products a row of FAs is added. The row of FAs takes the row of partial products and adds it to the result from the previous row of FAs. By the end of the final row of FAs all the partial products have been added together and the result of the multiplication has been completed.

Figure 1.3: Block diagram of an unsigned 8-bit array multiplier.

One of the advantages with the array multiplier is that it has a regular layout and short wires. The downside is that the delay of the multiplier increases linearly with the bitwidth of the multiplier. For each added bit, a new row of full adders is needed, to sum the partial products with the previous result. Further, the gate structure of the array causes lots of glitches and therefore the array multiplier tends to have high power dissipation [10].

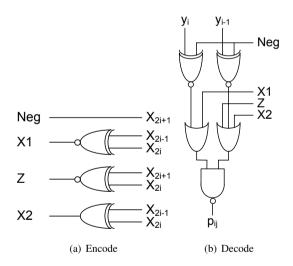

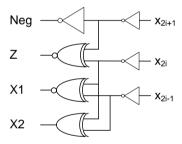

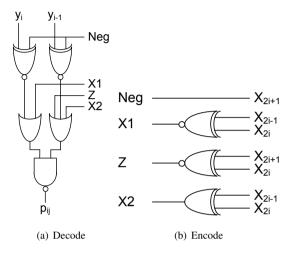

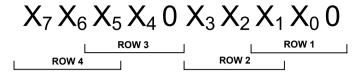

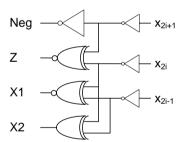

To reduce the delay, the number of rows of partial products that are generated can be reduced or a faster reduction circuit can be designed. Booth introduced a technique that reduces the number of generated partial products [11]. Instead of inspecting a single bit that can represent  $\{0,1\}$ , the technique inspects two bits of the multiplier-operand (X) and encodes them into  $\{-2,-1,0,1,2\}$ . The encoded bits are then multiplied with the multiplicand-operand (Y). The drawback of the Booth algorithm is that the number of rows with generated partial products is dependent on the input multiplier-operand. This makes the algorithm unsuitable for hardware implementation. MacSorley improved the technique by encoding three bits of the multiplier-operand into  $\{-2,-1,0,1,2\}$ . The modified-Booth algorithm [6] ensures that exactly half the number of partial product rows will be generated, compared to the number of partial product rows generated using 2-input AND-gates as in the array multiplier in Fig. 1.3.

The other option to reducing delay is to improve the reduction circuit. The most common implementation choice for high performance parallel multipliers is a logarithmic-depth reduction tree. With a logarithmic-depth reduction tree the critical path is reduced from being linearly dependent on the number of partial-product rows, as for the array multiplier, to a logarithmic dependency. An added benefit with logarithmic-depth reduction trees is that they produce less glitches than array multipliers and, thus, has lower power dissipation [10]. The drawback of logarithmic-depth reduction trees, such as the popular Dadda [12], Wallace [13], and TDM [14] trees, is that they have an irregular interconnect structure. The irregularity increases the design effort, since it makes them difficult to place and route.

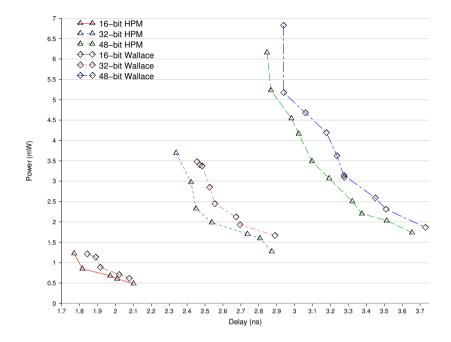

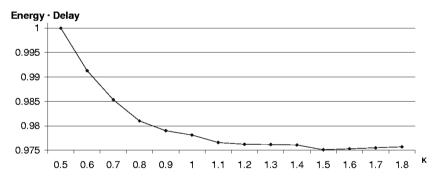

The first logarithmic-depth reduction tree with regular interconnect was introduced by Eriksson *et al.* with the High Performance Multiplier (HPM) [15]. The HPM reduction tree, which is a version of a Dadda tree [12], has the same logarithmic property as other logarithmic-depth reduction trees, with the advantage of a regular interconnect that makes it easier to place and route. An added benefit of the HPM reduction tree being a Dadda is that it performs better than the commonly used Wallace tree. Fig. 1.4 shows estimated power and delay values from placed and routed HPM and Wallace multipliers, in a 65 nm process technology. The figure clearly shows that the HPM reduction tree has both shorter delay and dissipates less power than a Wallace tree of equal bit-width.

A popular way of designing fast parallel multipliers is to combine the use of modified-Booth with a logarithmic-depth reduction tree, such as Wallace. The combination has the benefit of reducing the number of generated partial-product rows, which the logarithmic-depth reduction tree then quickly reduces to the inputs for the final adder. However, one disadvantage with the modified-Booth recoding scheme is that complex circuitry is needed to encode the multiplier-operand into  $\{-2, -1, 0, 1, 2\}$  and then to decode the multiplicand-operand. This introduces extra logic in the critical path. Taking into account that the critical path through a logarithmic-depth reduction tree is only reduced by at most two full adder delays, when combined with modified-Booth recoding, it is not obvious that the total delay of a modified-Booth multiplier implementation will be significantly reduced.

**Figure 1.4:** Delay and power estimates for a 65 nm process technology of multipliers based on the HPM and Wallace reduction tree.

In 1997 Callaway *et al.* presented a study [16] where they compare four different multiplier implementations. They come to the conclusion that the modified-Booth recoded Wallace tree is faster than a conventional Wallace tree. However, the modified-Booth recoded Wallace tree was found to dissipate more power and for the power-delay product the conventional Wallace tree was found to be the most efficient implementation.

The design practice used today is that of combining a logarithmic-depth reduction tree with modified-Booth recoding, even though Callaway *et al.* showed that a Wallace multiplier without modified-Booth recoding has a better power-delay product. An explanation can be that Callaway *et al.* made their study in a 2  $\mu$ m process technology with two metal layers and extrapolated delay and power for other multiplier sizes than the used 16-bit implementation. Since then, the process technology has progressed to gate lengths of less than 100 nm,

for which wire lengths have a more dominant role for both power and delay. Further, several new Booth-recoding circuits have been proposed that claim they reduce the critical path [17, 18], which are obviously not part of Callaway's study.

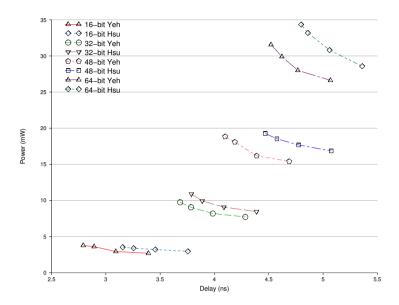

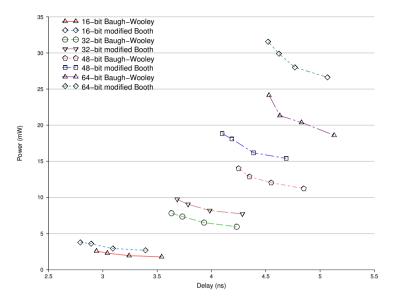

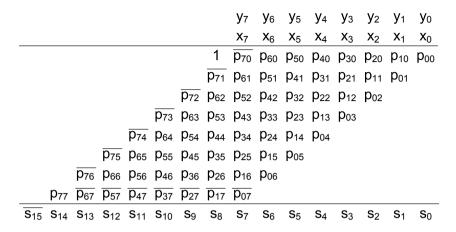

Paper C presents a detailed evaluation of signed integer multipliers that are based on the HPM reduction tree and either the modified-Booth [6] or Baugh-Wooley [7] algorithm. The Baugh-Wooley algorithm was chosen because it does not require complex recoding circuits that introduce extra logic in the critical path. The Baugh-Wooley algorithm is based on simple 2-input AND or NAND-gates for its partial-product generation. However, the Baugh-Wooley algorithm does not reduce the number of partial-product rows, as the modified-Booth algorithm does. The evaluation is based on two recent Booth-recoding circuits that have been found in the literature and have shown promising results in terms of short delay. The multipliers have been implemented using VHDL and synthesized, placed, and routed in both 130 nm and 65 nm process technologies, for accurate estimations on delay, power, and area. The evaluation shows that Baugh-Wooley multipliers of sizes from 8 to 64 bits are about 20% smaller, dissipates 25-40% less power, and are at most 4% slower than modified-Booth multipliers of equal size for the 130 nm process technology. 32-bit implementations of the multipliers in a 65 nm process technology show even larger differences in area (22%) and power (60%) with only a 3% difference in delay. The study shows that the delay difference of a Baugh-Wooley and modified-Booth multiplier of equal size is so small that the benefits of smaller area and reduced power make the Baugh-Wooley multiplier the obvious choice of the two.

# 1.2.2 Twin-Precision Multiplier

Many of the typical embedded applications work on streaming data, where the same operation is performed on each data item of the stream. This type of applications can benefit from a technique called Single Instruction Multiple Data (SIMD), which makes it possible to execute the same operation on multiple data items in parallel, with a single instruction. For this type of applications it is also common that they work with data-widths that are less than 32 bits, henceforth called narrow-width operations.

There have been several proposals on how to implement multipliers that efficiently support applications that can benefit from narrow-width SIMD multiplications *and* those that need full-precision multiplications. Since multipliers require large area, the techniques either combine several narrow-width multipliers to perform one full-width multiplication [19–22] or they partition the partial product generation of a full-width multiplier, such that it can perform narrow-width operations [23–27].

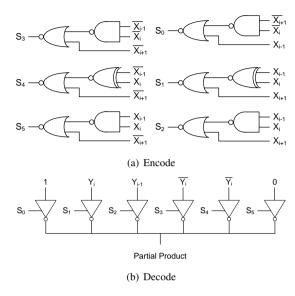

Most of the proposed multi-precision multiplier designs [19, 20, 22–24, 26, 27] utilize modified-Booth recoding. The modified-Booth recoder generates two's complement numbers which makes it necessary to sign extend the partial product rows. Sign extending the partial product rows would require a larger reduction tree. This can be avoided by special techniques that add only a few correction bits to each partial product row. However, the sign extension prevention bits add complexity when a multi-precision multiplier is to be designed, since these bits need to be added for each possible precision to be computed by the multiplier.

Two of the proposed multi-precision multipliers [21, 25] base their design on the Baugh-Wooley algorithm, instead of the modified-Booth algorithm. The two designs have taken two different approaches: Lin's [21] is a recursive multiplier constructed from several small multipliers that are combined to form larger multipliers, while Krithivasan *et al.* [25] partition the partial product generation and utilize the reduction tree of a full precision multiplier. Earlier studies [22, 28] have shown that a recursive multiplier is slower than a multiplier based on a logarithmic-depth reduction tree.

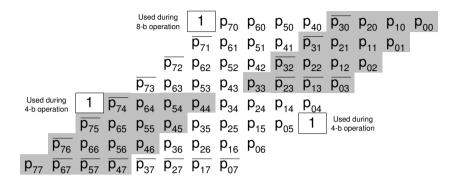

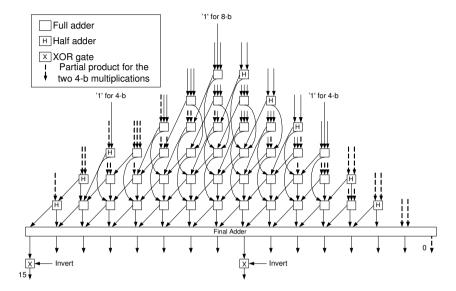

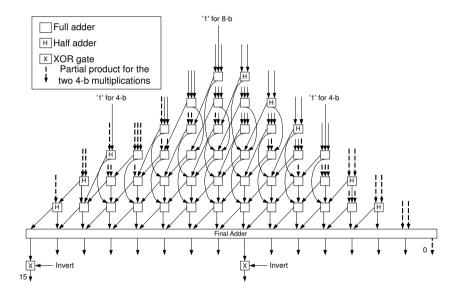

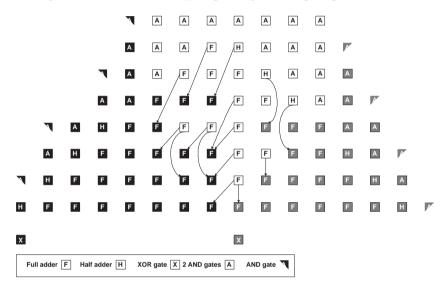

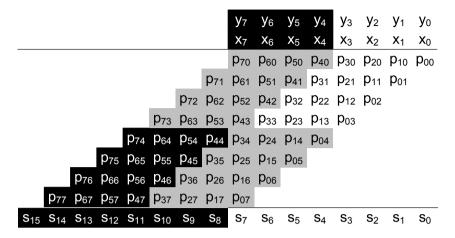

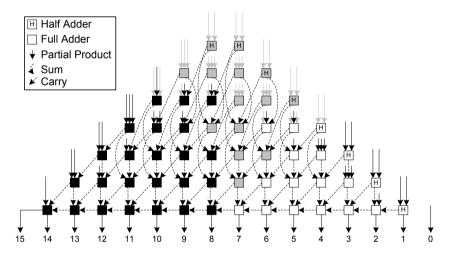

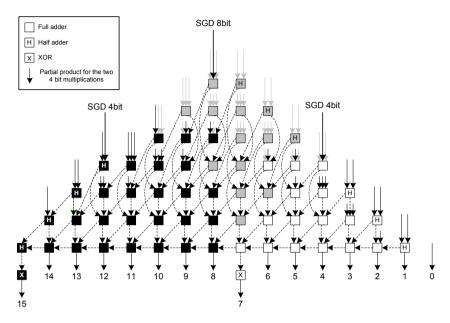

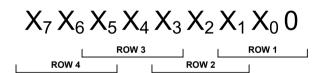

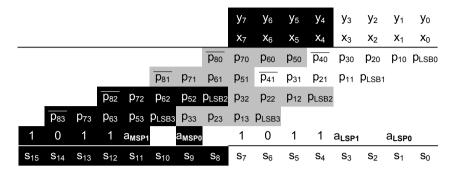

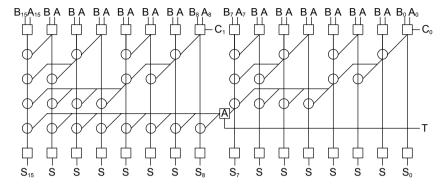

At about the same time as Krithivasan *et al.* presented their multi-precision multiplier [25], **Paper D** presented the twin-precision technique, which also partitions the partial product array of a Baugh-Wooley multiplier into sub-arrays. The twin-precision technique allows one *N*-bit, one *N*/2-bit, or two *N*/2-bit multiplication(s) to be computed on an *N*-bit multiplier. The technique tries to minimize the impact on delay and power of the *N*-bit multiplication by making as few modifications as possible to a conventional *N*-bit HPM multiplier. The low complexity of the Baugh-Wooley multiplier allows for a straightforward solution. The only modifications needed for narrow-width operation are *i*) the

capability of forcing parts of the partial product array to zero, ii) the capability of negating some of the partial products, and iii) the addition of two extra sign bits connected to the reduction tree. The modifications introduce at most a 3-input instead of 2-input AND-gate to the critical path of the N-bit multiplier. The added logic is limited to N-2 XOR-gates, N/2 half-adder gates, and the replacement of 3/4 of all  $N \times N$  2-input AND-gates to 3-input AND-gates. The twin-precision technique also allows a single N/2-bit multiplication to be computed. This allows for power savings when an application does not need the full precision of an N-bit multiplier, but cannot pack several multiplications together for SIMD operation.

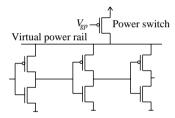

When a twin-precision multiplier operates on *N*/2-bit operands, large parts of the multiplier are idle. **Paper E** presents a reconfigurable power gating technique that can be used to power off the inactive parts of the multiplier. The study shows that significant reduction in leakage power with limited impact on delay can be achieved by a customized power supply grid. In this particular study, the total power of a 16-bit twin-precision multiplier was reduced by 11% when executing 8-bit multiplications for a 130 nm process technology.

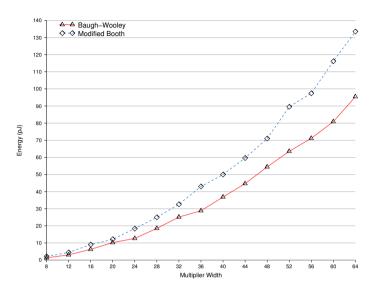

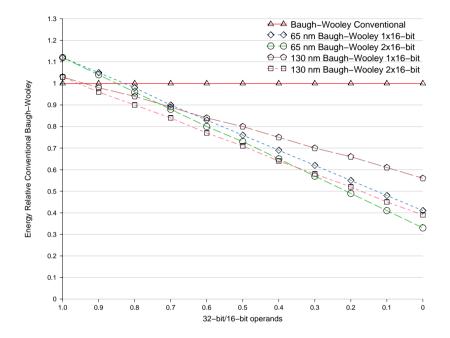

The modified-Booth algorithm is complex and gives rise to many special cases that need to be handled in a multi-precision multiplier. This complicates the design of multi-precision modified-Booth multipliers, which has a negative impact on their performance and power. In **Paper F** a twin-precision modified-Booth multiplier is compared to a twin-precision Baugh-Wooley multiplier. The comparison shows that for a 130 nm process technology a twin-precision modified-Booth multiplier is slower, dissipates more power, and is larger than a twin-precision Baugh-Wooley multiplier of equal bit-width. The study clearly shows that the modified-Booth algorithm is not suitable when implementing multi-precision multipliers.

The intention of the twin-precision technique is that it should be possible, during the design of a system, to replace a conventional multiplier with a twin-precision multiplier. The added flexibility should come at a minimal impact on the performance and power of the overall design. The twin-precision multiplier has therefore been designed to have a small or negligible impact on the performance of a conventional multiplier, when executing full-precision, *N*-bit, multi-

plications. **Paper F** presents a case study where the multiplier of an embedded 32-bit general-purpose processor is replaced by a twin-precision multiplier. The results show that the twin-precision technique has negligible impact on the performance of a general-purpose processor. Further, its SIMD capabilities allow, in this case, a Fast Fourier Transform (FFT) application to be executed 15% faster and with a 14% decrease in energy dissipation.

# 1.3 Task Scheduling for Multi-Core Architectures

The relentless demands for higher performance, e.g. to be able to provide high-definition (HD) video or increase the number of advanced features in mobile devices, have lead to that the performance of a single processor core is not sufficient. This is mainly due to five major challenges, so called walls, that limit the performance of a single processor core.

- *I) Instruction Level Parallelism Wall* A single core solution suffers from limited Instruction Level Parallelism (ILP) that can be found and exploited in sequential programs. It has been shown [29, 30] that it is difficult to reach an ILP of more than ten instructions per cycle without unlimited hardware resources.

- II) Memory Wall The increasing imbalance between the performance of a processor and its memory subsystem has lead to what has been termed the memory wall [31]. The large imbalance has lead to that the performance of the processor is unexploited, since it has to wait for data from memory when performing data accesses.

- III) Power Wall As the process technology is scaled down the leakage power has started to drastically increase. The increasing power dissipation has lead to that improvements in performance need to be matched with improvements in efficiency as well. Without improving the efficiency, the power dissipation of a single processor core will continue to increase to prohibitive levels [32].

- *IV)* Clock Frequency Wall Increasing the frequency of a processor typically requires deeper pipelines and more power. However, a longer pipeline increases the chance of resource conflicts, which will make the processor stall and the

penalty for miss speculations. Further, the optimal logic depth of a pipeline stage is about six to eight fan-out-of-four (FO4) delays [33], which puts a limit to the number of stages a design can be divided into. Therefore, increasing the frequency other than by process technology scaling is not easily achieved.

V) Complexity Wall – The design of a single core is becoming ever more complex and the complexity of the most advanced processors has reached such levels that they are extremely difficult to design and verify. Pollack observed that for a lead microprocessor the number of transistors was increased with a factor of about two for each new process generation, while the performance was only improved by 40% [32, 34].

With a multi-core architecture many of the challenges associated with a single-core architecture can be avoided. For a multi-core architecture it is possible to design a relatively simple processor that has a good tradeoff between power and performance. Desired system performance can then be achieved by instantiating several of these cores, which can also help to reduce the power dissipation. By adding a second core to a single processor system the theoretical performance is doubled. It is then possible to trade some of the performance gain against lower power dissipation. This can be achieved due to the quadratic dependency between power and the supply voltage, while the frequency has only a linear dependency to the supply voltage. Lowering the supply voltage reduces the power more than it reduces the performance. A parallel application consists of several threads, which makes it possible for a processor to switch to another thread instead of waiting on a memory accesses. With several threads it is also not necessary to increase the ILP of each thread to increase performance, one can instead increase the number of threads and the number of cores executing them.

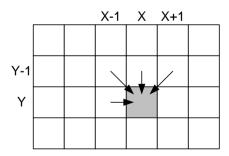

Multi-core architectures require that the applications are parallelized for them to take advantage of the available performance. The parallelization consists of partitioning an application into a number of tasks (threads) that can then be distributed over several cores, henceforth called task scheduling, in order to accelerate application performance. Many of the current solutions [35–37] rely on software for partitioning the application into tasks and to distribute them. A software solution can be efficient as long as the overhead for creating and

distributing a new task is much smaller than the task itself. As the number of cores increases an application will have to be partitioned into more and, thus, smaller tasks. As the tasks become smaller, the overhead of a software solution can become prohibitively large. A natural step to reduce the task scheduling overhead is to add some type of hardware support. There exist several hardware techniques [38–41] that tries to address this problem. Kumar *et al.* proposed to add hardware queues for storing and distributing tasks [38] and showed that they are on average 70-110% faster than software task scheduling, for a set of fine-grained parallel applications.

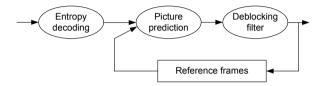

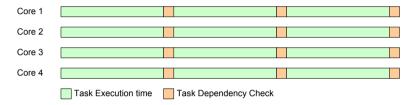

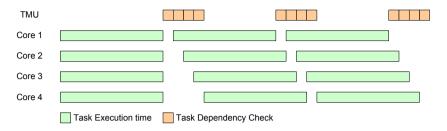

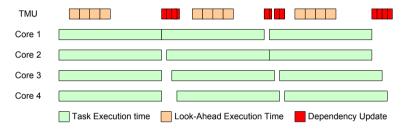

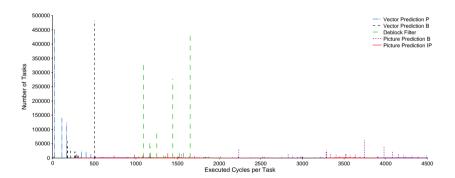

Partitioning of applications from the multimedia domain will generally introduce dependencies between the tasks, which force the tasks to be executed in a certain order. For this kind of application workloads it is not enough to be able to efficiently create tasks and distribute them. It is also necessary to keep track of when a new task can be created. The algorithms needed for keeping track of the creation of tasks are not necessarily complex, but they can introduce large overheads. In **Paper G** it is shown that the code for calculating what task to be executed next accounts for 9% of the total execution of the parallelized sections of a Super HD H.264 decoder. The paper presents a task management unit that can offload and execute the task dependency code in parallel with other tasks. The task management unit is shown to reduce the overhead with 40-50%, compared to task scheduling through the use of a task queue.

# 1.4 Conclusion

Building embedded systems can be very complicated. For an efficient implementation it is necessary to consider all levels of an embedded system, from applications down to the actual implementation.

This thesis addresses issues of how to efficiently schedule tasks of an application onto different cores in a multi-core system, as well as scheduling of individual instructions onto a single core. Scheduling of instructions is limited by the hardware-software interface, which dictates in what ways a compiler/programmer can take advantage of available hardware resources. The envisioned two-tier instruction set in the FlexSoC project questions the limitation

of control given by conventional instructions sets, such as those for applicationspecific, general-purpose, and very-long-instruction-word processors. The envisioned two-tier instruction set gives the compiler/programmer expressive control of the hardware, which can be taken advantage of when scheduling instructions. The two-tier instruction set also opens up for new architectural features to be considered, such as the flexible interconnect and the ease of integrating hardware accelerators into the datapath of a FlexCore. However, the performance of a new architecture depends on the components it is built of. Arithmetic circuits are extensively used in all digital systems and are often timing critical. In particular, the integer multiplier is slow, power hungry, and large, relative to other arithmetic circuits. Implementation techniques that can improve the flexibility, performance, and efficiency of integer multipliers have therefore been presented. Further, as the process technologies continue to scale, leakage power has become a great concern when designing energy efficient embedded systems. To address the problem of increased power dissipation, a customized power gating technique for integer multipliers is presented.

This thesis shows the complexity involved and solutions to several relevant issues that need to be addressed when designing embedded systems.

# **Bibliography**

- [1] ARM Limited, 110 Fulbourn Road Cambridge, England CB1 9NJ, ARM Architecture Reference Manual., i edition, July 2005.

- [2] Steve Leibson, Designing SOCs with Configured Cores: Unleashing the Tensilica Xtensa and Diamond Cores, Morgan Kaufmann Publishers, 2006, ISBN-13: 978-0-12-372498-4.

- [3] John Hughes, Kjell Jeppson, Per Larsson-Edefors, Mary Sheeran, Per Stenström, and Lars "J." Svensson, "FlexSoC: Combining Flexibility and Efficiency in SoC Designs," in *Proceedings of the IEEE NorChip Conference*, 2003.

- [4] Bita Gorjiara and Daniel Gajski, "Custom Processor Design Using NISC: a Case-Study on DCT Algorithm," in *Workshop on Embedded Systems for Real-Time Multimedia*, September 2005, pp. 55–60.

BIBLIOGRAPHY 19

[5] Bita Gorjiara, Mehrdad Reshadi, and Daniel Gajski, "Designing a Custom Architecture for DCT Using NISC Design Flow," in Asia and South Pacific Conference on Design Automation, 2006, pp. 116–117.

- [6] O.L.MacSorley, "High Speed Arithmetic in Binary Computers," in *Proceedings of the IRE*, January 1961, vol. 49, pp. 67–97.

- [7] Charles R. Baugh and Bruce A. Wooley, "A Two's Complement Parallel Array Multiplication Algorithm," *IEEE Transactions on Computers*, vol. 22, pp. 1045– 1047, December 1973.

- [8] David A. Patterson and John L. Hennessy, Computer Organization & Design, The Hardware/Software Interface, Morgan Kaufman Publishers Inc., 2nd edition, 1998.

- [9] "Embedded Microprocessor Benchmark Consortium," http://www.eembc. org.

- [10] Jeroen Leijten, Jef van Meerbergen, and Jochen Jess, "Analysis and Reduction of Glitches in Synchronous Networks," in *Proceedings of the European Design and Test Conference*, March 1995, pp. 398–403.

- [11] Andrew D. Booth, "A Signed Binary Multiplication Technique," *Quarterly Journal of Mechanics and Applied Mathematics*, vol. 4, no. 2, pp. 236–240, 1951.

- [12] Luigi Dadda, "Some Schemes for Parallel Adders," *Alta Frequenza*, vol. 34, no. 5, pp. 349–356, May 1965.

- [13] Christopher S. Wallace, "A Suggestion for a Fast Multiplier," *IEEE Transactions on Electronic Computers*, vol. 13, pp. 14–17, February 1964.

- [14] Vojin G. Oklobdzija, David Villeger, and Simon S. Liu, "A Method for Speed Optimized Partial Product Reduction and Generation of Fast Parallel Multipliers Using an Algorithmic Approach," *IEEE Transactions on Computers*, vol. 45, no. 3, pp. 294–306, March 1996.

- [15] Henrik Eriksson, Per Larsson-Edefors, Mary Sheeran, Magnus Själander, Daniel Johansson, and Martin Schölin, "Multiplier Reduction Tree with Logarithmic Logic Depth and Regular Connectivity," in *IEEE International Symposium on Circuits and Systems*, May 2006, pp. 5–8.

- [16] Thomas K. Callaway and Jr. Earl E. Swartzlander, "Power-Delay Characteristics of CMOS Multipliers," in *Proceedings of the 13th IEEE Symposium on Computer Arithmetic*, June 1997, pp. 26–32.

[17] Wen-Chang Yeh and Chein-Wei Jen, "High-Speed Booth Encoded Parallel Multiplier Design," *IEEE Transactions on Computers*, vol. 49, no. 7, pp. 692–701, July 2000.

- [18] Steven K. Hsu, Sanu K. Mathew, Mark A. Anders, Bart R. Zeydel, Vojin G. Oklobdzija, Ram K. Krishnamurthy, and Shekhar Y. Borkar, "A 110 GOPS/W 16-bit Multiplier and Reconfigurable PLA Loop in 90-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 1, pp. 256–264, January 2006.

- [19] K.C. Tang, Angus K. M. Wu, Anthony S. Fong, and Derek C. W. Pao, "Integrated Partition Integer Execution Unit for Multimedia and Conventional Applications," in *Proceedings of the IEEE Conference on Electronics, Circuits, and Systems*, September 1998, vol. 2, pp. 103–107.

- [20] Martin S. Schmookler, Michael Putrino, Charles Roth, Mukesh Sharma, Anh Mather, Jon Tyler, Huy Van Nguyen, Mydung N. Pham, and Jeff Lent, "A Low-Power, High-Speed Implementation of a PowerPC<sup>TM</sup>Microprocessor Vector Extension," in *Proceedings of the 14th IEEE Symposium on Computer Arithmetic*, April 1999, pp. 12–19.

- [21] Rong Lin, "Reconfigurable parallel inner product processor architectures," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 9, no. 2, pp. 261–272, April 2001.

- [22] Pedram Mokrian, Majid Ahmadi, Graham Jullien, and W.C. Miller, "A Reconfigurable Digital Multiplier Architecture," in *Proceedings of the IEEE Canadian Conference on Electrical and Computer Engineering*, 2003, pp. 125–128.

- [23] Dimitri Tan, Albert Danysh, and Michael Liebelt, "Multiple-Precision Fixed-Point Vector Multiply-Accumulator Using Shared Segmentation," in *Proceedings of the 16th IEEE Symposium on Computer Arithmetic*, June 2003, pp. 12–19.

- [24] Ya-Lan Tsao, Wei-Hao Chen, Ming Hsuan Tan, Maw-Ching Lin, and Shyh-Jye Jou, "Low-Power Embedded DSP Core for Communication Systems," *EURASIP Journal on Applied Signal Processing*, vol. 2003, no. 1, pp. 1355–1370, 2003.

- [25] Shankar Krithivasan and Michael J. Schulte, "Multiplier Architectures for Media Processing," in *Proceedings of Signals the 37th IEEE Asilomar Conference on Systems and Computers*, November 2003, vol. 2, pp. 9–12.

- [26] Alber Danysh and Dimitri Tan, "Architecture and Implementation of a Vector/SIMD Multiply-Accumulate Unit," *IEEE Transactions on Computers*, vol. 5, no. 4, pp. 284–293, May 2005.

BIBLIOGRAPHY 21

[27] Yan Sun, Lanfei Dong, Daheng Yue, Shaoqing Li, and Minxuan Zhang, "Multiple-Precision Subword-Parallel Multiplier Using Correction-Value Merging Technique," in *Proceedings of the 7th IEEE International Conference on ASIC*, October 2007, pp. 48–51.

- [28] Albert N. Danysh and Earl E. Swartzlander Jr., "A Recursive Fast Multiplier," in *Proceedings of the 32nd Asilomar Conference on Signals, Systems and Computers*, November 1998, vol. 1, pp. 197–201.

- [29] David V. Wall, "Limits of Instruction-Level Parallelism," Tech. Rep. WRL-93-6, HP Labs Technical Reports, November 1993.

- [30] Hsien-Hsin Lee, Youfeng Wu, and Gary Tyson, "Quantifying Instruction-Level Parallelism Limits on an EPIC Architecture," in *Proceedings of the IEEE Interna*tional Symposium on Performance Analysis of Systems and Software, April 2000, pp. 21–27.

- [31] William A. Wulf and Sally A. McKee, "Hitting the Memory Wall: Implications of the Obvious," *ACM SIGARCH Computer Architecture News*, vol. 23, no. 1, pp. 20–24, 1995.

- [32] Patrick P. Gelsinger, "Microprocessors for the new Millennium: Challenges, Opportunities, and new Frontiers," in *Technical Digest of the IEEE International Conference on Solid-State Circuits Conference*, February 2001, pp. 22–25.

- [33] M.S Hrishikesh, Norman P. Jouppi, Keith I. Farkas, Doug Burger, Stephen W. Keckler, and Premkishore Shivakumar, "The Optimal Logic Depth per Pipeline Stage is 6 to 8 FO4 Inverter Delays," in *Proceedings of the 29th International Symposium on Computer Architecture*, May 2002, pp. 14–24.

- [34] Fred J. Pollack, "New Microarchitecture Challenges in the Coming Generations of CMOS Process Technologies," Keynote. 32nd IEEE International Symposium on Microarchitecture, November 1999.

- [35] Intel Corporation, Intel Thread Building Blocks, 2007, Revision 1.6.

- [36] OpenMP Architecture Review Board, *OpenMP Application Program Interface*, November 2004, Version 2.5.

- [37] Message Passing Interface Forum, MPI-2: Extensions to the Message-Passing Interface, July 1997.

- [38] Sanjeev Kumar, Christopher J. Hughes, and Anthony Nguyen, "Carbon: Architectural Support for Fine-Grained Parallelism on Chip Multiprocessors," in *IEEE International Symposium on Computer Architecture*, June 2007, pp. 734–740.

22 INTRODUCTION

[39] Kyriakos Stavrou, Costas Kyriacou, Paraskevas Evripidou, and Pedro Trancoso, "Chip Multiprocessor Based on Data-Driven Multithreading Model," *International Journal of High Performance Systems Architecture*, vol. 1, no. 1, pp. 24–43, 2007.

- [40] Pelge Avieli, Oded Rubenov, and Nomrod Bayer, "Designing a Central Synchronization/Scheduling Unit For Multiprocessors," in *IEEE Convention of the Electrical and Electronic Engineers*, April 2000, pp. 495–498.

- [41] Nimrod Bayer and Ran Ginosar, "High Flow-Rate Synchronizer/Scheduler Apparatus and Method for Multiprocessors," April 1993.

M. Thuresson, **M. Själander**, M. Björk, L. Svensson, P. Larsson-Edefors, and P. Stenstöm

FlexCore: Utilizing Exposed Datapath Control for Efficient Computing

Springer Journal of Signal Processing Systems Accepted for publication, March 4, 2008.

# FlexCore: Utilizing Exposed Datapath Control for Efficient Computing

We introduce FlexCore, the first exemplar of an architecture based on the Flex-SoC framework. Comprising the same datapath units found in a conventional five-stage pipeline, the FlexCore has an exposed datapath control and a flexible interconnect to allow the datapath to be dynamically reconfigured as a consequence of code generation. Additionally, the FlexCore allows specialized datapath units to be inserted and utilized within the same architecture and compilation framework.