THESIS FOR THE DEGREE OF LICENTIATE OF ENGINEERING

## **Efficient Reconfigurable Multipliers Based on the Twin-Precision Technique**

Magnus Själander

Division of Computer Engineering

Department of Computer Science and Engineering

CHALMERS UNIVERSITY OF TECHNOLOGY

Göteborg, Sweden 2006

### Efficient Reconfigurable Multipliers Based on the Twin-Precision Technique

Magnus Själander

Copyright © Magnus Själander, 2006.

Technical report 12L

ISSN 1652-876X

Department of Computer Science and Engineering

VLSI Research Group

Division of Computer Engineering Chalmers University of Technology SE-412 96 GÖTEBORG, Sweden

Phone: +46 (0)31-772 10 00

Author e-mail: magnus@sjalander.com

### Cover:

Picture by the author that shows the twin-precision technique applied to the reduction tree of the High Performance Multiplier.

Printed by Chalmers Reproservice Göteborg, Sweden 2006

## **Efficient Reconfigurable Multipliers Based on the Twin-Precision Technique**

Magnus Själander

Division of Computer Engineering, Chalmers University of Technology

### ABSTRACT

During the last decade of integrated electronic design ever more functionality has been integrated onto the same chip, paving the way for having a whole system on a single chip. The strive for ever more functionality increases the demands on circuit designers that have to provide the foundation for all this functionality. The desire for increased functionality and an associated capability to adapt to changing requirements, has led to the design of reconfigurable architectures. With an increased interest and use of reconfigurable architectures there is a need for flexible and reconfigurable computational units that can meet the demands of high speed, high throughput, low power, and area efficiency.

Multiplications are complex to implement and they continue to give designers headaches when trying to efficiently implement multipliers in hardware. Multipliers are therefore interesting to study, when investigating how to design flexible and reconfigurable computational units.

In this thesis the results from investigations on flexible multipliers are presented. The new twin-precision technique, which was developed during this work, makes a multiplier able to adapt to different requirements. By adapting to actual multiplication bitwidth using the twin-precision technique, it is possible to save power, increase speed and double computational throughput. The investigations have also led to the conclusion that the long used and popular modified-Booth multiplier is inferior in all aspects to the less complex Baugh-Wooley multiplier. During this work, a VHDL multiplier generator was created and made publicly available.

Keywords: High-Speed, Low-Power, Multipliers, Reconfigurable, Twin-precision, VLSI

### **Preface**

Parts, but far from all, of the contributions presented in this thesis have previously been accepted to conferences or submitted to journals.

- ▶ M. Själander, H. Eriksson, and P. Larsson-Edefors, "An Efficient Twin-Precision Multiplier," in *IEEE International Conference on Computer Design*, San Jose, United States of America, October 10–13, 2004, pp. 507–510.

- ▶ M. Själander, M. Draždžiulis, P. Larsson-Edefors, and H. Eriksson, "A Low-Leakage Twin-Precision Multiplier Using Reconfigurable Power Gating," in *IEEE International Symposium on Circuits and Systems*, Kobe, Japan, May 23–26, 2005, pp. 1654–1657.

- M. Själander and P. Larsson-Edefors, "A Power-Efficient and Versatile Modified-Booth Multiplier," in Swedish System-on-Chip Conference, Tammsvik, Sweden, April 18–19 2005.

- ▶ M. Själander and P. Larsson-Edefors, "Comprehensive Evaluation of a Modified-Booth Multiplier with Logarithmic Reduction Tree," submitted to *IEEE Transaction on Very Large Scale Integrated Sys*tems, January 20th 2006.

- ▶ H. Eriksson, P. Larsson-Edefors, M. Sheeran, M. Själander, D. Johansson, and M. Schölin "Multiplier Reduction Tree with Logarithmic Logic Depth and Regular Connectivity" in *IEEE International Symposium on Circuits and Systems* Island of Kos, Greece, May 21–24, 2006

iv PREFACE

### Acknowledgments

I am grateful to the following people for what they have done for me, for my career, and for this thesis.

- ▷ Professor Per Larsson-Edefors who is not only excellent to discuss technical aspects of my research with, but who cares about me, who helps during the long and late hours before a deadline, who goes for lunch with me and who is a friend to trust.

- ▷ Lic. Eng. Mindaugas Draždžiulis, for teaching me everything I know about leakage reduction and for our fruitful research collaborations that led us to Japan.

- ► Martin Thuresson, my personal DJ, that has had to withstand me during our years at Chalmers (or was it the other way around). For many long and interesting discussions and numerous poker nights.

- ▷ Lic. Eng. Daniel Andersson for interesting conversations and for sharing my newly found interest in playing squash.

- Dr. Henrik Eriksson for helping me start my research on twin-precision multipliers by basing it on the High Performance Multiplier and all the support for understanding the finer details of a multiplier.

- ▷ Dr. Daniel Eckerbert for his wast knowledge in circuit design and for introducing me to the tools that are so critical for our line of research.

- > Dr. Jim Nilsson for our early brainstorm on reconfigurable multipliers.

- Sten Gunnarsson, for putting me in contact with Professor Per Larsson-Edefors and for the time spent together hanging from a rock-face in the western parts of Sweden.

- Conny Olsson, for his consultation on the finer details of the layout of this thesis and for always welcoming me to his home, when I'm visiting my hometown Östersund.

- Magnus Almgren, Ana Bosque Arbiol, Charlotta, Bååth, Minh Quang Do, Jochen Hollman, Wolfgang John, Henrik Larsson, Jessica Leong, Lina Ohlsson, Greger Sundqvist, and Marcus Östberg, my good friends.

- ▶ Pierre Kleberger for interesting discussions on Linux related topics.

- ▶ Lars Kollberg for always prioritizing problems with the EDA tools.

- ▷ Camilla Berglund, Lars Johansson, and Mikael Samuelsson for their excellent work on the implementation of a modified-Booth multiplier.

- ➤ The Swedish Foundation for Strategic Research (SSF) for their funding of my position at Chalmers University of Technology.

- My beloved grandmother, Sonja Kallin, for always supporting me and for letting me stay at her place when I was working a year in Östersund, thus, allowing me to start my academic career.

- ▶ My uncle, Harald Kallin, for being a role model and inspiring me to take

my Masters degree in Computer Engineering.

- ▶ My parents Thomas and Ingeborg Själander and my brother Lars Själander who have supported me through life and made this thesis possible.

I dedicate this thesis to the memories of my dear friends Ulf Allberg and Annika Jämtlid and their daughter Lovisa, who were enjoying the weather in Khao Lak when the tsunami came 29th of December, 2004.

Magnus Själander Göteborg, February 2006

### Contents

| A۱ | bstrac | t       |                                                           | i   |

|----|--------|---------|-----------------------------------------------------------|-----|

| Pı | eface  |         |                                                           | iii |

| A  | cknow  | ledgme  | ents                                                      | v   |

| Ι  | IN     | ГROD    | UCTION                                                    | 1   |

| 1  | Intr   | oductio | n                                                         | 3   |

|    | 1.1    | Twin-l  | Precision Fundamentals                                    | 6   |

|    |        | 1.1.1   | A First Implementation                                    | 9   |

|    |        | 1.1.2   | An HPM Implementation                                     | 11  |

|    | 1.2    | A Bau   | gh-Wooley Implementation                                  | 11  |

|    |        | 1.2.1   | Algorithms for Baugh-Wooley                               | 12  |

|    |        | 1.2.2   | Twin-Precision Using the Baugh-Wooley Algorithm           | 13  |

|    | 1.3    | A Mod   | dified-Booth Implementation                               | 16  |

|    |        | 1.3.1   | Algorithms for Modified Booth                             | 16  |

|    |        | 1.3.2   | Twin-Precision Using the modified-Booth Algorithm $$ . $$ | 17  |

|    | 1.4    | Simula  | ation Setups                                              | 22  |

|    |        | 1.4.1   | Synthesized Baugh-Wooley Netlist                          | 23  |

|    |        | 1.4.2   | Synthesized Modified-Booth Netlist                        | 23  |

|    | 1.5    | Result  | s and Discussion                                          | 25  |

|    |        | 1.5.1   | Power Dissipation                                         | 25  |

|    |        |         |                                                           |     |

viii CONTENTS

|    |                                          | 1.5.2                                                                       | Delay                                            | 27                                                               |

|----|------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------|

|    |                                          | 1.5.3                                                                       | Area                                             | 30                                                               |

|    |                                          | 1.5.4                                                                       | Modified Booth versus Baugh-Wooley               | 31                                                               |

|    |                                          | 1.5.5                                                                       | Power Reduction by the Use of Power Gating       | 32                                                               |

|    |                                          | 1.5.6                                                                       | The Impact of the Final Adder on Delay           | 34                                                               |

|    | 1.6                                      | A Case                                                                      | e Study                                          | 34                                                               |

|    |                                          | 1.6.1                                                                       | Total Execution Time                             | 36                                                               |

|    |                                          | 1.6.2                                                                       | Total Electric Energy Dissipation                | 36                                                               |

|    |                                          | 1.6.3                                                                       | Area                                             | 39                                                               |

|    |                                          | 1.6.4                                                                       | Summary                                          | 39                                                               |

|    | 1.7                                      | Conclu                                                                      | isions                                           | 40                                                               |

|    | Bibli                                    | iography                                                                    | y                                                | 41                                                               |

|    |                                          |                                                                             |                                                  |                                                                  |

| II | PΔ                                       | PERS                                                                        |                                                  | 45                                                               |

|    | -1.                                      | II DIK                                                                      | ,                                                |                                                                  |

| 2  | PAP                                      | ER I                                                                        |                                                  | 49                                                               |

|    | 2.1                                      | Introdu                                                                     | action                                           | 50                                                               |

|    | 2.2                                      | Design                                                                      | Exploration                                      | 51                                                               |

|    |                                          | 2.2.1                                                                       | Tree Multiplier                                  | 52                                                               |

|    |                                          | 222                                                                         | Cinned Multiplication Assembly to Double Western | 52                                                               |

|    |                                          | 2.2.2                                                                       | Signed Multiplication According to Baugh-Wooley  | 53                                                               |

|    | 2.3                                      |                                                                             | Adder                                            | 53<br>54                                                         |

|    | 2.3<br>2.4                               | Final A                                                                     |                                                  |                                                                  |

|    |                                          | Final A                                                                     | Adder                                            | 54                                                               |

|    | 2.4<br>2.5                               | Final A Simula Conclu                                                       | Adder                                            | 54<br>56                                                         |

| 2  | 2.4<br>2.5<br>Bibli                      | Final A<br>Simula<br>Conclu                                                 | Adder                                            | 54<br>56<br>58<br>58                                             |

| 3  | 2.4<br>2.5<br>Bibli                      | Final A Simula Conclusiography ER II                                        | Adder                                            | <ul><li>54</li><li>56</li><li>58</li><li>58</li><li>63</li></ul> |

| 3  | 2.4<br>2.5<br>Bibli                      | Final A Simula Conclusiography ER II Introdu                                | Adder                                            | <ul><li>54</li><li>56</li><li>58</li><li>58</li><li>63</li></ul> |

| 3  | 2.4<br>2.5<br>Bibli                      | Final A Simula Conclusiography ER II Introdu Prelim                         | Adder                                            | 54<br>56<br>58<br>58<br><b>63</b><br>64                          |

| 3  | 2.4<br>2.5<br>Bibli                      | Final A<br>Simula<br>Conclusiography<br>ER II<br>Introdu<br>Prelim<br>3.2.1 | Adder                                            | 54<br>56<br>58<br>58<br><b>63</b><br>64<br>64                    |

| 3  | 2.4<br>2.5<br>Bibli<br>PAP<br>3.1<br>3.2 | Final A Simula Conclusiography ER II Introdu Prelim 3.2.1 3.2.2             | Adder                                            | 54<br>56<br>58<br>58<br><b>63</b><br>64<br>64<br>66              |

| 3  | 2.4<br>2.5<br>Bibli                      | Final A Simula Conclusiography  ER II Introdu Prelim 3.2.1 3.2.2 Power      | Adder                                            | 54<br>56<br>58<br>58<br><b>63</b><br>64<br>64                    |

| CONTENTS | i |

|----------|---|

|          |   |

|   | 3.5  | Conclu  | asions                                            | 74 |

|---|------|---------|---------------------------------------------------|----|

|   | Bibl | iograph | y                                                 | 74 |

| 4 | PAP  | ER III  |                                                   | 79 |

|   | 4.1  | Introdu | action                                            | 79 |

|   | 4.2  | Prelim  | inaries                                           | 80 |

|   |      | 4.2.1   | Basic Unsigned Twin-Precision Multiplication      | 80 |

|   |      | 4.2.2   | The Modified-Booth Algorithm                      | 82 |

|   | 4.3  | Suppo   | rting Twin Precision in Modified Booth            | 83 |

|   | 4.4  | A Mod   | dified-Booth Twin-Precision Multiplier            | 84 |

|   | 4.5  | Simula  | ation and Results                                 | 87 |

|   | 4.6  | Conclu  | asion                                             | 89 |

|   | Ack  | nowledg | gment                                             | 90 |

|   | Bibl | iograph | y                                                 | 90 |

| 5 | PAP  | ER IV   |                                                   | 93 |

|   | 5.1  | Introdu | action                                            | 94 |

|   | 5.2  | Algori  | thms and Implementations                          | 95 |

|   |      | 5.2.1   | Algorithms for Modified Booth                     | 95 |

|   |      | 5.2.2   | Modified-Booth Implementation                     | 97 |

|   |      | 5.2.3   | Algorithms for Baugh-Wooley                       | 98 |

|   |      | 5.2.4   | Baugh-Wooley Implementation                       | 98 |

|   | 5.3  | Gate-L  | evel Analysis                                     | 99 |

|   | 5.4  | Simula  | ations and Results                                | 03 |

|   |      | 5.4.1   | Synthesized Modified Booth Netlist                | 04 |

|   |      | 5.4.2   | Synthesized Baugh-Wooley Netlist                  | 06 |

|   |      | 5.4.3   | Delay Comparison                                  | 07 |

|   |      | 5.4.4   | Power Comparison                                  | 08 |

|   |      | 5.4.5   | Area Comparison                                   | 09 |

|   | 5.5  | Conclu  | asions                                            | 10 |

|   | Ack  | nowledg | gment                                             | 10 |

|   | App  | endix . |                                                   | 10 |

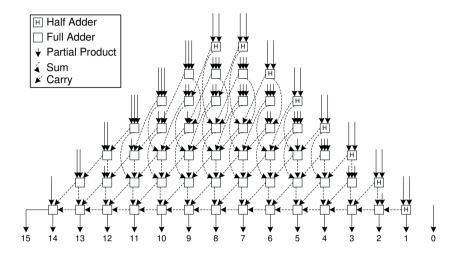

|   |      | The H   | igh Performance Multiplier (HPM) Reduction Tree 1 | 10 |

x CONTENTS

|   | Bibli | ography | ·                      |  | • |  |  |  | • |  |  | • | 111 |

|---|-------|---------|------------------------|--|---|--|--|--|---|--|--|---|-----|

| 5 | PAP   | ER V    |                        |  |   |  |  |  |   |  |  |   | 115 |

|   | 6.1   | Introdu | ction                  |  |   |  |  |  |   |  |  |   | 115 |

|   | 6.2   | The HF  | PM Reduction Tree      |  |   |  |  |  |   |  |  |   | 116 |

|   |       | 6.2.1   | Design Method          |  |   |  |  |  |   |  |  |   | 117 |

|   |       | 6.2.2   | Layout Organization .  |  |   |  |  |  |   |  |  |   | 120 |

|   | 6.3   | Evaluat | tion                   |  |   |  |  |  |   |  |  |   | 123 |

|   |       | 6.3.1   | Timing Comparison (i)  |  |   |  |  |  |   |  |  |   | 123 |

|   |       | 6.3.2   | Timing Comparison (ii) |  |   |  |  |  |   |  |  |   | 124 |

|   |       | 6.3.3   | Power Comparison (iii) |  |   |  |  |  |   |  |  |   | 124 |

|   | 6.4   | Conclu  | sion                   |  |   |  |  |  |   |  |  |   | 125 |

|   | Ackr  | nowledg | ment                   |  |   |  |  |  |   |  |  |   | 125 |

|   | Ribli | ography | ī                      |  |   |  |  |  |   |  |  |   | 125 |

## List of Figures

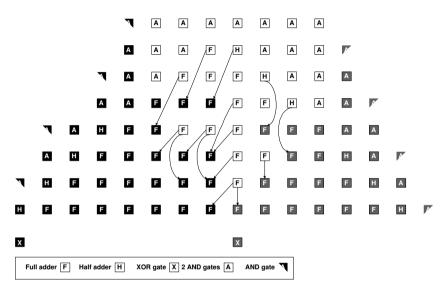

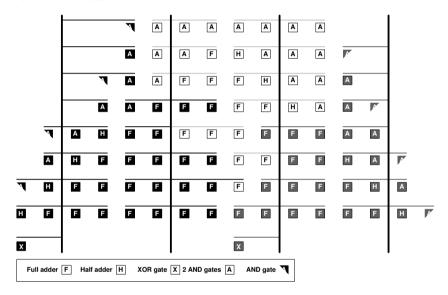

| 1.1 | illustration of an unsigned 8-bit multiplication                                                                                                                                                                                                                                                                     | b  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Illustration of an unsigned 8-bit multiplication, where the precision of the operands is smaller than the precision of the multiplication. Unused bits of operands and product, as well as unused partial products, are shown in gray                                                                                | 7  |

| 1.3 | Illustration of an unsigned 8-bit multiplication, where a 4-bit multiplication, shown in white, is computed in parallel with a second 4-bit multiplication, shown in black.                                                                                                                                          | 8  |

| 1.4 | Block diagram of an unsigned 8-bit array multiplier                                                                                                                                                                                                                                                                  | 10 |

| 1.5 | Block diagram of an unsigned 8-bit twin-precision array multiplier. The TP signal is used for controlling if one full-precision multiplication should be computed or two 4-bit multiplications should be computed in parallel                                                                                        | 11 |

| 1.6 | Block diagram of an unsigned 8-bit twin-precision multiplier that is based on the regular HPM reduction tree. A 4-bit multiplication, shown in white, can be computed in parallel with a second 4-bit multiplication, shown in black. For simplicity of the figure the AND/NAND gates for partial product generation |    |

|     | is not shown and a ripple carry is used as final adder                                                                                                                                                                                                                                                               | 12 |

| 1.7 | Illustration of a signed 8-bit multiplication, using the Baugh-                                                                                                                                                                                                                                                      |    |

|     | Wooley algorithm                                                                                                                                                                                                                                                                                                     | 13 |

xii LIST OF FIGURES

| 1.8  | Illustration of a signed 8-bit multiplication, using the Baugh          |     |

|------|-------------------------------------------------------------------------|-----|

|      | Wooley algorithm, where a 4-bit multiplication, shown in white,         |     |

|      | is computed in parallel with a second 4-bit multiplication, shown       | 1.4 |

|      | in black.                                                               | 14  |

| 1.9  | Block diagram of a signed 8-bit multiplication, using the Baugh         |     |

|      | Wooley algorithm, where a 4-bit multiplication, shown in white,         |     |

|      | is computed in parallel with a second 4-bit multiplication, shown       | 15  |

| 1 10 | in black.                                                               |     |

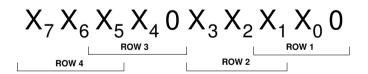

| 1.10 | 8-bit modified-Booth encoding                                           | 17  |

| 1.11 | Illustration of a signed 8-bit multiplication using the modified-       |     |

|      | Booth algorithm                                                         | 18  |

| 1.12 | Illustration of a signed 8-bit multiplication using the modified-       |     |

|      | Booth algorithm                                                         | 18  |

| 1.13 | Block diagram of a signed 8-bit multiplication using the modified-      |     |

|      | Booth algorithm, where a 4-bit multiplication, shown in white,          |     |

|      | is computed in parallel with a second 4-bit multiplication, shown       |     |

|      | in black                                                                | 20  |

| 1.14 | Encode and decode circuit for modified Booth                            | 21  |

| 1.15 | Encoding scheme for two 4-bit multiplications                           | 21  |

| 1.16 | Buffered encode circuit for fanout reduction                            | 24  |

| 1.17 | Impact on the total delay for different fanout of the encoder           | 25  |

| 1.18 | Total power in W for conventional Baugh-Wooley and mod-                 |     |

|      | ified Booth as well as twin-precision versions of both, when            |     |

|      | operating at 200 MHz. For the twin-precision implementa-                |     |

|      | tions, the power for a single $N/2$ multiplication is also given. $\ .$ | 27  |

| 1.19 | Total delay in ns for a conventional Baugh-Wooley implemen-             |     |

|      | tation and its twin-precision counterpart                               | 28  |

| 1.20 | Total delay in ns for a conventional modified-Booth imple-              |     |

|      | mentation and its twin-precision counterpart                            | 29  |

| 1.21 | Relative area for conventional Baugh-Wooley and modified-               |     |

|      | Booth multipliers versus twin-precision versions of both                | 30  |

LIST OF FIGURES xiii

| 1.22 | Total area for conventional Baugh-Wooley and modified-Booth       |    |

|------|-------------------------------------------------------------------|----|

|      | multipliers as well as twin-precision versions of both            | 31 |

| 1.23 | Baugh-Wooley TP static power portion of total power               | 32 |

| 1.24 | Power grid for an 8-bit twin-precision Baugh-Wooley imple-        |    |

|      | mentation                                                         | 33 |

| 1.25 | The delay profile for the inputs of the final adder for a twin-   |    |

|      | precision 32-bit Baugh-Wooley multiplier. The delay for a         |    |

|      | specific bit is the average of the A and B input                  | 35 |

| 1.26 | Total execution time for 1000 multiplications where the per-      |    |

|      | centage of low precision multiplications is varied                | 37 |

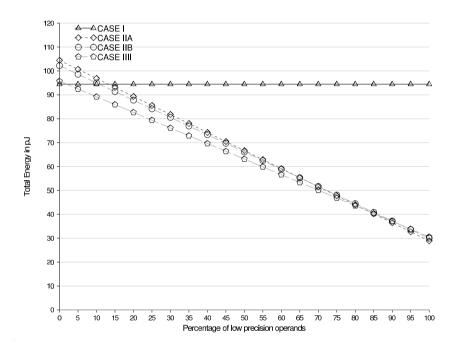

| 1.27 | Total energy expended, with the percentage of low-precision       |    |

|      | multiplications being varied                                      | 38 |

| 2.1  | Partial product representation of a 4-b multiplication in an 8-b  |    |

|      | multiplier                                                        | 52 |

| 2.2  | Partitioned tree of an 8-b multiplier                             | 53 |

| 2.3  | Example showing the inverted partial product bits of two signed   |    |

|      | 4-b multiplications within a signed 8-b multiplication            | 54 |

| 2.4  | Signed 8-b multiplier capable of doing two signed 4-b multi-      |    |

|      | plications using Baugh-Wooley                                     | 55 |

| 2.5  | Example of 31-b final adder for a 16-b twin-precision multiplier. | 55 |

| 3.1  | Partial product representation of an 8-bit multiplication. When   |    |

|      | performing a 4-bit multiplication in a conventional multiplier    |    |

|      | only one quarter of the logic gates are performing any useful     |    |

|      | operations (the grey regions). The twin-precision technique       |    |

|      | rearranges logic to greatly reduce power dissipation and de-      |    |

|      | lay for 4-bit multiplications. Also, this technique allows the    |    |

|      | logic gates, which are not used in the 4-bit multiplication tak-  |    |

|      | ing place in the grey region, to perform a second, independent    |    |

|      | 4-bit multiplication (the black regions)                          | 65 |

| 3.2  | Signed 8-bit twin-precision Baugh-Wooley multiplier               | 66 |

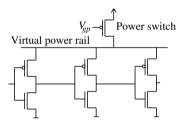

| 3.3  | The SCCMOS technique applied to an inverter chain                 | 67 |

xiv LIST OF FIGURES

| 3.4 | Power-gating regions of an 8-bit TP multiplier. When one $N/2$ - |     |

|-----|------------------------------------------------------------------|-----|

|     | bit multiplication is performed, the power switches in black     |     |

|     | and white regions are turned off. When two concurrent $N/2$ -bit |     |

|     | multiplications are performed, the power switches in the white   |     |

|     | region are turned off. Finally, when an N-bit multiplication is  |     |

|     | performed, the power switches in all regions are turned on       | 68  |

| 3.5 | The power supply grid of the 8-bit TP multiplier. Here, virtual  |     |

|     | power rails are routed horizontally, whereas external power      |     |

|     | and ground rails are routed vertically.                          | 70  |

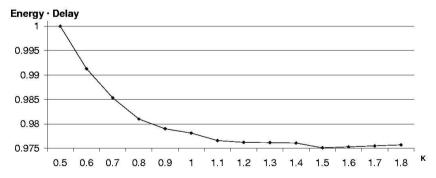

| 3.6 | Normalized energy-delay product for different power switch       |     |

|     | sizes                                                            | 72  |

| 4.1 | Partial-product representation of an 8-bit multiplication with   |     |

|     | two 4-bit multiplications                                        | 81  |

| 4.2 | 8-bit encoding.                                                  | 82  |

| 4.3 | 8-bit modified-Booth multiplication                              | 83  |

| 4.4 | Two 4-bit modified-Booth multiplications                         | 84  |

| 4.5 | 8-bit twin-precision modified-Booth multiplier                   | 85  |

| 4.6 | Decoder circuit that optionally sets partial products to zero    | 86  |

| 4.7 | Encoding scheme for two 4-bit multiplications                    | 86  |

| 5.1 | Illustration of an 8-bit modified-Booth multiplication           | 96  |

| 5.2 | 8-bit modified-Booth multiplier using an HPM reduction tree.     |     |

|     | For simplicity, the modified-Booth recoding logic is not shown.  |     |

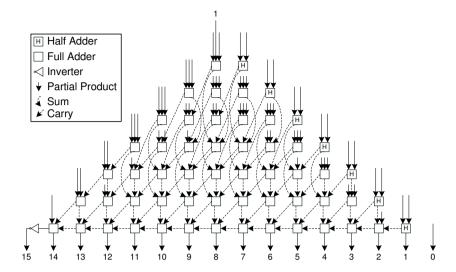

|     | Furthermore, a simple ripple-carry adder is used as final adder. | 97  |

| 5.3 | Encode and decode circuit for modified Booth                     | 98  |

| 5.4 | Illustration of an 8-bit Baugh-Wooley multiplication             | 99  |

| 5.5 | 8-bit Baugh-Wooley multiplier using an HPM reduction tree.       |     |

|     | For simplicity, the AND/NAND gates for partial-product gen-      |     |

|     | eration are not shown. Furthermore, a simple ripple-carry        |     |

|     | adder is used as final adder                                     | 100 |

LIST OF FIGURES xv

| 5.6  | Delay profile for the inputs to the final adder for the 32-bit Baugh-Wooley and modified-Booth cases. The delay for a specific bit is the average of the two full-adder inputs of each                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | significance level of a final adder                                                                                                                                                                                                                                                                      |

| 5.7  | Buffered encode circuit for fanout reduction                                                                                                                                                                                                                                                             |

| 5.8  | Impact on the total delay of different encoder-to-decoder fanout. 106                                                                                                                                                                                                                                    |

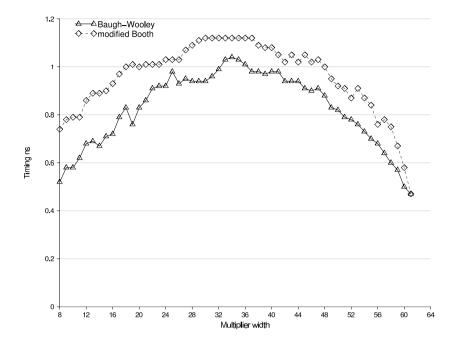

| 5.9  | Total delay (ns) of the Baugh-Wooley and modified-Booth multipliers                                                                                                                                                                                                                                      |

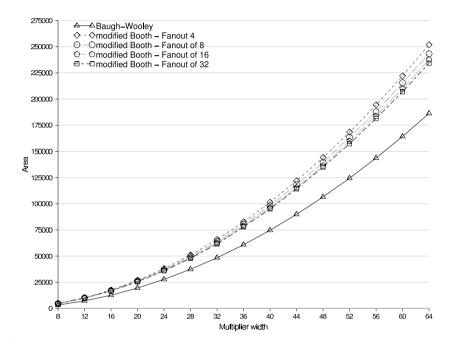

| 5.10 | Power (W) of the Baugh-Wooley and modified-Booth multipliers. The power for modified Booth is shown with respect to several different fanouts of the encoder                                                                                                                                             |

| 5.11 | Area of the Baugh-Wooley and modified-Booth multipliers.  The area for modified Booth is shown with respect to different fanout of the encoder                                                                                                                                                           |

| 5.12 | The regular reduction tree of the HPM for an unsigned 8-bit multiplier                                                                                                                                                                                                                                   |

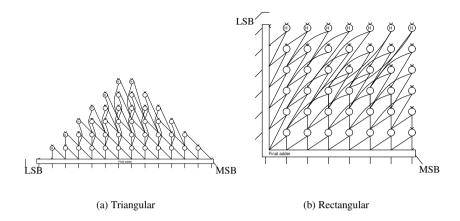

| 6.1  | The four steps leading to an 8-b Dadda multiplier. Two dots that are tied together by a line represent a sum and a carry. If the line is crossed, it is a half adder producing the sum and carry, otherwise it is a full adder. The cell type is also indicated by the number of bits that are encircled |

| 6.2  | The six steps leading to an 8-b HPM tree. Note that the six steps do <i>not</i> imply a linear logic depth. The logic depth is still logarithmic                                                                                                                                                         |

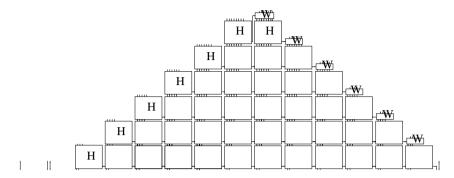

| 6.3  | Different cell placements for the HPM reduction tree. The rectangular shape has larger total wire length                                                                                                                                                                                                 |

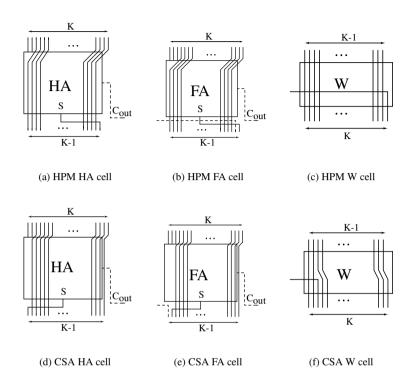

| 6.4  | The overall reduction structure used to build both the HPM and CSA multipliers. Boxes marked H contain half adders and wiring, unmarked boxes contain full adders and wiring, and cells marked W contain only wiring                                                                                     |

xvi LIST OF FIGURES

| 6.5 | The routing patterns for full adder, half adder and wiring cells |

|-----|------------------------------------------------------------------|

|     | in the HPM and the CSA multipliers. In both cases, these cells   |

|     | are combined into the structure shown in Fig. 6.4. As long       |

|     | as primary partial-product bits remain to be compressed, the     |

|     | HPM compresses only those, ignoring sum and carry bits as        |

|     | long as possible. This is in contrast to the CSA, in which       |

|     | most FA cells consume one primary partial-product bit for        |

|     | each compression stage                                           |

## Part I INTRODUCTION

# Introduction

Multiplication is a complex arithmetic operation, which is reflected in its relatively high signal propagation delay, high power dissipation and large area requirement. When choosing a multiplier for a digital system, the bitwidth of the multiplier is required to be at least as wide as the largest operand of the applications that are to be run on that digital system. The bitwidth of the multiplier is, therefore, often much larger than its operands, which leads to excessive power dissipation and long delay. This could partially be remedied by having several multipliers, each with a specific bitwidth, and using the particular multiplier with the smallest bitwidth that is large enough for the current multiplication. Such a scheme would assure that a multiplication would be computed on a multiplier that has been optimized in terms of power and delay for that specific bitwidth. Several multipliers with the same bitwidth could also be

used in a Single Instruction Multiple Data (SIMD) fashion, in order to increase throughput, thus reducing total execution time for multiplication-intensive applications. However, using several multipliers with different bitwidths would not be an efficient solution because of area overhead due to having multiple multiplier instances, and power overhead due to static power dissipation of inactive multipliers.

Ever increasing performance requirements make it challenging to implement multipliers that are efficient in terms of throughput, delay, power, and area for a wide range of bitwidths.

There have been several studies on operand bitwidths of integer applications and it has been shown that for the SPECint95 benchmarks more than 50% of the instructions are instructions where both operands are less than or equal to 16 bits [1] (henceforth called narrow-width operations). This property has been explored to save power, through operand guarding. In operand guarding the most significant bits of the operands are not switched, thus power is saved in the arithmetic unit when multiple narrow-width operations are computed consecutively [2, 3]. Narrow-width operands have also been used to increase instruction throughput, by computing several narrow-width operations in parallel on a full-width datapath [1, 4].

Brooks *et al.* [1] showed that power dissipation can be reduced by gating of the upper part of narrow-width operands. For the SPECint95 and media benchmarks, the power reduction of an operand guarded integer unit was 54% and 58%, respectively, which accounts for a total power reduction of around 5-6% for an entire datapath.

Loh [4] and Brooks *et al.* [1] have also investigated the possibility of increasing execution bandwidth by double pumping (doubling the throughput) an integer Arithmetic Logic Unit (ALU) with narrow-width operations. Loh showed a 7% speedup for the SPECint2000 benchmarks by using a simple 64-bit ALU, which excluded the multiplier, in parallel with four simple 16-bit ALUs that share a 64-bit routing. Brooks *et al.* did a similar investigation, where they envisioned a 64-bit adder that could be separated into four 16-bit adders by breaking the carry chain.

There have been several studies on operand guarding for multipliers. Huang *et al.* [2] introduced a two-dimensional operand guarding for array multipliers, resulting in a power dissipation that was only 33% of a conventional array multiplier. Han *et al.* [3] did a similar investigation on a 32-bit Wallace multiplier and was able to reduce the switching activity by 72% with the use of 16-bit operand guarding.

While there have been a lot of work on simple schemes for operand guarding, work to increase the throughput of a multiplier is more scarce. Achieving double throughput for a multiplier is not as straightforward as for an adder, where the carry chain can be cut at the appropriate place to achieve narrowwidth additions. It is of course possible to use several multipliers, where at least two have narrow bitwidth, and let them share the same routing, as in the work of Loh. But this scheme has several drawbacks: *i*) The total area of the multipliers would increase, since several multiplier units are used. ii) The use of several multipliers increases the fanout of the signals that drive the inputs of the multipliers. Higher fanout means longer delays and/or higher power dissipation. iii) There would be a need for multiplexers that connect the active multiplier to the result route. These multiplexers would be in the critical path, increasing total delay as well as power dissipation. Work has been done to use 4:2-reduction stages to combine small tree multipliers into larger multipliers [5, 6]. This can be done in several stages, creating a larger multiplier out of smaller for each extra 4:2 reduction stage. The desired bitwidth of the multiplication is then obtained by using multiplexers. This technique requires extra reduction stages for the larger multipliers, which has a negative impact on the delay for these.

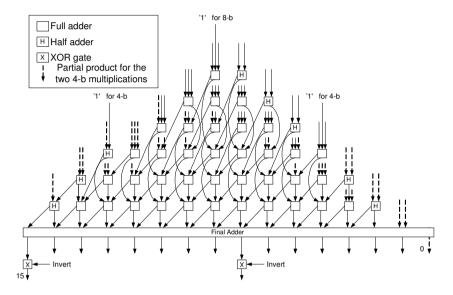

We present the twin-precision technique [7] that offers the same power reduction as operand guarding *and* the possibility of double-throughput multiplications. The twin-precision technique is an efficient way of achieving double throughput in a multiplier with low area overhead and with practically no delay penalty. We show how to apply the twin-precision technique on signed multipliers based on the regular High Performance Multiplier (HPM) reduction tree. The two algorithms for signed multiplications that have been used are Baugh-Wooley and the popular modified-Booth algorithm.

(1.1)

$p_{ij} = y_i x_j$

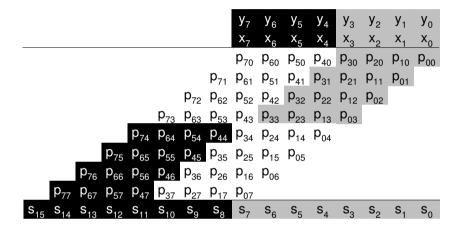

### 1.1 Twin-Precision Fundamentals

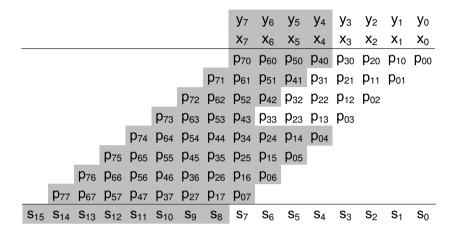

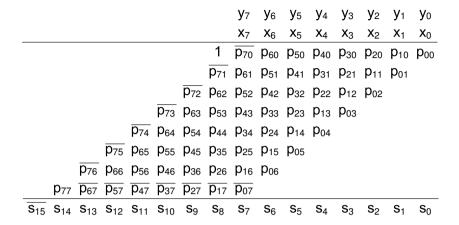

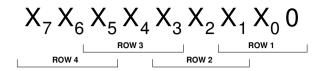

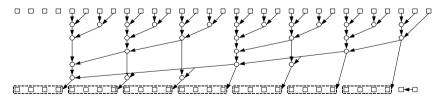

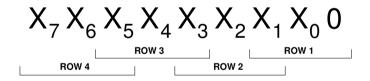

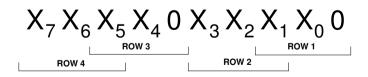

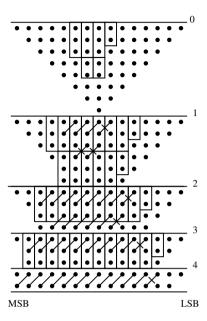

For a first analysis of the twin-precision technique, the discussion will be based on an illustration of an unsigned binary multiplication. In an unsigned binary multiplication each bit of one of the operands, called the multiplier, is multiplied with the second operand, called multiplicand (Eq. 1.1). That way one row of partial products is generated. Each row of partial products is shifted according to the position of the bit of the multiplier, forming what is commonly called the partial-product array. Finally, partial products that are in the same column are summed together, forming the final result. An illustration of an 8-bit multiplication is shown in Fig. 1.1.

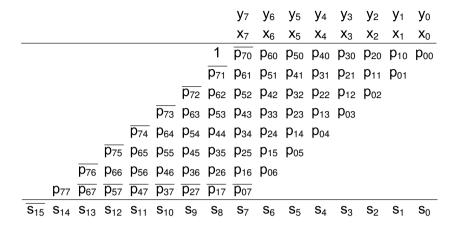

$X_5$  $X_4$  $X_3$ Χ2  $p_{70}$   $p_{60}$   $p_{50}$   $p_{40}$   $p_{30}$   $p_{20}$   $p_{10}$   $p_{00}$  $p_{71}$   $p_{61}$   $p_{51}$   $p_{41}$   $p_{31}$   $p_{21}$   $p_{11}$   $p_{01}$  $p_{72}$   $p_{62}$   $p_{52}$   $p_{42}$   $p_{32}$   $p_{22}$   $p_{12}$   $p_{02}$  $p_{73} \ p_{63} \ p_{53} \ p_{43} \ p_{33} \ p_{23} \ p_{13} \ p_{03}$ p<sub>74</sub> p<sub>64</sub> p<sub>54</sub> p<sub>44</sub> p<sub>34</sub> p<sub>24</sub> p<sub>14</sub> p<sub>04</sub> P<sub>75</sub> P<sub>65</sub> P<sub>55</sub> P<sub>45</sub> P<sub>35</sub> P<sub>25</sub> P<sub>15</sub> P<sub>05</sub>  $p_{76}$   $p_{66}$   $p_{56}$   $p_{46}$   $p_{36}$   $p_{26}$   $p_{16}$   $p_{06}$  $p_{77} \ p_{67} \ p_{57} \ p_{47} \ p_{37} \ p_{27} \ p_{17}$  $S_{15}$   $S_{14}$   $S_{13}$   $S_{12}$   $S_{11}$   $S_{10}$   $S_{9}$  $S_8$  $S_7$  $S_6$  $S_5$  $S_4$  $S_3$ S2  $S_1$ So

Figure 1.1: Illustration of an unsigned 8-bit multiplication.

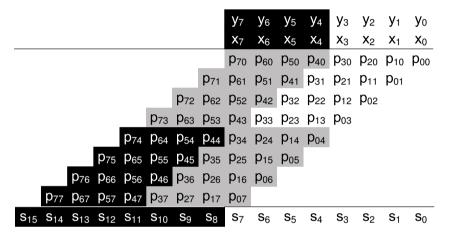

Let us look at what happens when the precision of the operands is smaller than the multiplier we intend to use. In this case, the most significant bits of the operands will only contain zeros, thus large parts of the partial-product array will consist of zeros. Further, the summation of the most significant part of the partial-product array and the most significant bits of the final result will only consist of zeros. An illustration of an 8-bit multiplication, where the precision of the operands is four bits, is shown in Fig. 1.2.

**Figure 1.2:** Illustration of an unsigned 8-bit multiplication, where the precision of the operands is smaller than the precision of the multiplication. Unused bits of operands and product, as well as unused partial products, are shown in gray.

Fig. 1.2 shows that large parts of the partial products are only containing zeros and are, thus, not contributing with any useful information for the final result. What if these partial products could be utilized for a second, concurrent multiplication?

Since partial products of the same column are summed together, it would not be wise to use any of the partial products that are in the same column as the multiplication that is already computed. Looking closer at the 4-bit multiplication marked in white in Fig. 1.2, one can also observe that the column at position  $S_7$  should not be used either. This is because that column might have a carry from the active part of the partial-product array that will constitute the final  $S_7$ . Altogether this makes only the partial products in the most significant part of the partial-product array available for a second multiplication.

In order to be able to use the partial products in the most significant part, there has to be a way of setting their values. For this we can use the most significant bits of the operands, since these are not carrying any useful information. If we are only looking at the upper half of the operands, the partial products generated from these bits are the ones shown in black in Fig. 1.3. By setting the other partial products to zero, it is then possible to perform two multiplications within the same partial-product array, without changing the way the summation of the partial-product array is done. How the partial products, shown in gray, can be set to zero will be investigated in the implementation section later on.

**Figure 1.3:** Illustration of an unsigned 8-bit multiplication, where a 4-bit multiplication, shown in white, is computed in parallel with a second 4-bit multiplication, shown in black.

Assume, for now, that there is a way of setting unwanted partial products to zero, then it suddenly becomes possible to partition the multiplier into two smaller multipliers that can compute multiplications in parallel. In the above illustrations the two smaller multiplications have been chosen such that they are of equal size. This is not necessary for the technique to work. Any size of the two smaller multiplications can be chosen, as long as the precision of the two smaller multiplications together are equal or smaller than the full precision  $(N_{FULL})$  of the multiplication, Eq. 1.2. To be able to distinguish between the two smaller multiplications, they are referred to as the multiplication in the Least Significant Part (LSP) of the partial-product array with size  $N_{LSP}$ , shown

in white, and the multiplication in the Most Significant Part (MSP) with size  $N_{MSP}$ , shown in black.

$$N_{FULL} \ge N_{LSP} + N_{MSP} \tag{1.2}$$

It is functionally possible to partition the multiplier into even more multiplications. For example, it would be possible to partition a 64-bit multiplier into four 16-bit multiplications. Given a number K of low precision multiplications their total size need to be smaller or equal to the full precision multiplication.

$$N_{FULL} \ge \sum_{i=1}^{K} N_i \tag{1.3}$$

For the rest of this investigation, the precision of the two smaller multiplications will be equal and half the precision (N/2) of the full precision (N) of the multiplier.

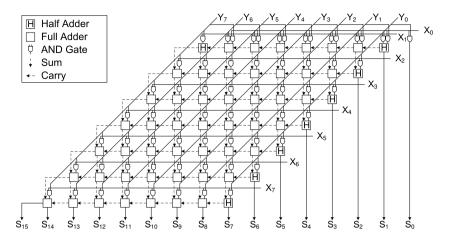

### 1.1.1 A First Implementation

The basic operation of generating a partial product is that of a 1-bit multiplication using a 2-input AND gate, where one of the input signals is one bit of the multiplier and the second input signal is one bit of the multiplicand. The summation of the partial products can be done in many different ways, but for this investigation we are only interested in parallel multipliers that are based on 3:2 full adders<sup>1</sup>. For this first implementation an array of adders will be used because of its close resemblance to the previously used illustration of a multiplication.

In the previous section we assumed that there is a way of setting unwanted partial products to zero. This is easily accomplished by changing the 2-input AND gate to a 3-input AND gate, where the extra input can be used for a control signal. Of course, only the AND gates of the partial products that has to be set to zero need to be changed to a 3-input version. During normal operation when a full-precision multiplication is executed the control signal is set to high,

<sup>&</sup>lt;sup>1</sup>Higher-radix compression is compatible with our strategy.

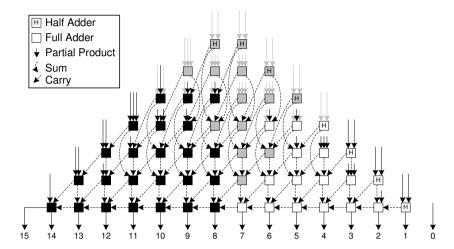

Figure 1.4: Block diagram of an unsigned 8-bit array multiplier.

thus all partial products are generated as normal and the array of adders will sum them together and create the final result. When the control signal is set to low the unwanted partial products will become zero. Since the summation of the partial products are not overlapping, there is no need to modify the array of adders. The array of adders will produce the result of the two multiplications in the upper and lower part of the final output. The block diagram of an 8-bit twin-precision array multiplier capable of computing two 4-bit multiplications is shown in Fig. 1.5. The two multiplications have been colored in white and black to visualize what part of the adder array is used for what multiplication.

More flexibility might be wanted, like the possibility to compute a single low-precision multiplication or two parallel low-precision multiplications, within the same multiplier. This can be done by changing the 2-input AND gates for the partial product generation of the low-precision multiplication as well. In the array multiplier in Fig. 1.5, the AND gates for the 4-bit MSP multiplication, shown in black, can be changed to 3-input AND gates to which a second control signal can be added. Assuming the multiplier is divided into two equal parts, this modification makes it possible to either compute an N-bit, a single N/2-bit or two concurrent N/2-bit multiplications.

**Figure 1.5:** Block diagram of an unsigned 8-bit twin-precision array multiplier. The TP signal is used for controlling if one full-precision multiplication should be computed or two 4-bit multiplications should be computed in parallel.

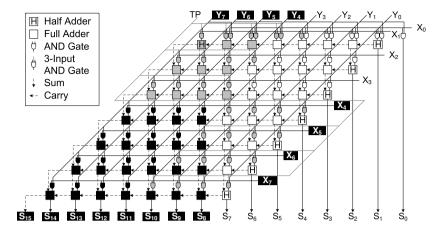

### 1.1.2 An HPM Implementation

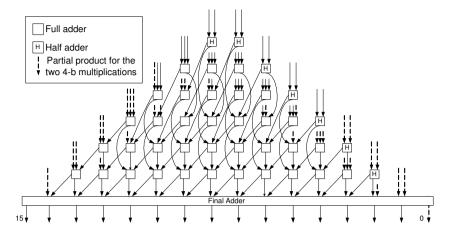

The array multiplier in the previous section was only used to show the principle of the twin-precision technique. For high-speed and/or low-power implementations, a logarithmic reduction tree such as the TDM [8], Dadda [9], Wallace [10] or HPM [11] is preferred for summation of the partial products. A logarithmic reduction tree has the benefit that the logic depth is shorter. Further, a logarithmic tree has fewer glitches making it less power dissipating. A twin-precision implementation based on the regular HPM reduction tree is shown in Fig. 1.6.

### 1.2 A Baugh-Wooley Implementation

In the previous section, the concept of twin precision was introduced by looking at an unsigned multiplication. However, for many applications signed multiplications are needed and consequently an unsigned multiplier is of limited use. In this section a twin-precision multiplier based on the Baugh-Wooley (BW) algorithm will be presented.

**Figure 1.6:** Block diagram of an unsigned 8-bit twin-precision multiplier that is based on the regular HPM reduction tree. A 4-bit multiplication, shown in white, can be computed in parallel with a second 4-bit multiplication, shown in black. For simplicity of the figure the AND/NAND gates for partial product generation is not shown and a ripple carry is used as final adder.

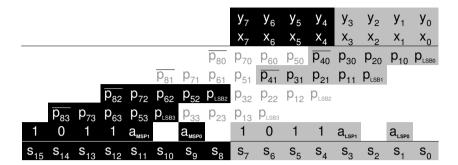

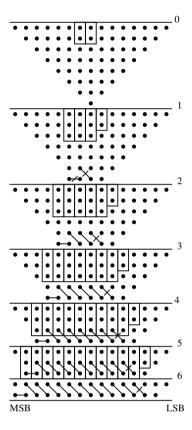

### 1.2.1 Algorithms for Baugh-Wooley

The BW algorithm [12] is a relative straightforward way of doing signed multiplications. Fig. 5.4 illustrates the algorithm for an 8-bit case, where the partial-product array has been reorganized according the the scheme of Hatamian [13]. The creation of the reorganized partial-product array comprises three steps: i) the most significant partial product of the first N-1 rows and the last row of partial products except the most significant has to be negated, ii) a constant one is added to the Nth column, iii) the most significant bit (MSB) of the final result is negated.

**Figure 1.7:** Illustration of a signed 8-bit multiplication, using the Baugh-Wooley algorithm.

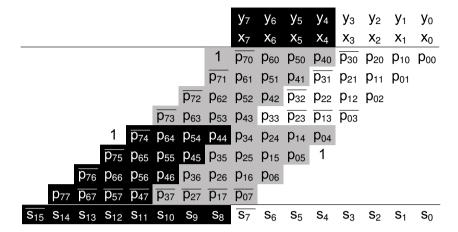

### 1.2.2 Twin-Precision Using the Baugh-Wooley Algorithm

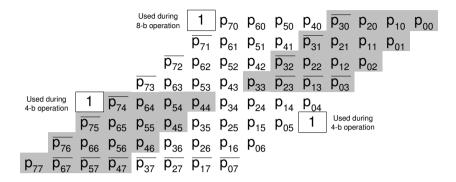

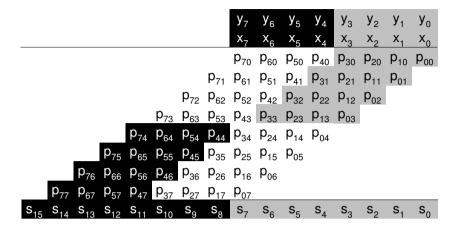

To combine twin-precision with BW is not as simple as for the unsigned multiplication, where only parts of the partial products needed to be set to zero. To be able to compute two signed N/2 multiplications, it is necessary to make a more sophisticated modification of the partial-product array. Fig. 1.8 shows an illustration of an 8-bit BW multiplication, where two 4-bit multiplications have been depicted in white and black.

When comparing the illustration of Fig. 1.7 with that of Fig. 1.8 one can see that the only modification needed to compute the 4-bit multiplication in the MSP of the array is an extra sign bit '1' in column  $S_{12}$ . For the 4-bit multiplication in the LSP of the array, there is a need for some more modifications. Looking at the active partial-product array of the 4-bit LSP multiplication (shown in white), we see that the most significant partial product of all rows, except the last, needs to be negated. For the last row it is the opposite, here all partial products, except the most significant, are negated. Also for this multiplication a sign bit '1' is needed, but this time in column  $S_4$ . Finally the MSB of the result needs to be negated to get the correct result of the two 4-bit multiplications.

**Figure 1.8:** Illustration of a signed 8-bit multiplication, using the Baugh-Wooley algorithm, where a 4-bit multiplication, shown in white, is computed in parallel with a second 4-bit multiplication, shown in black.

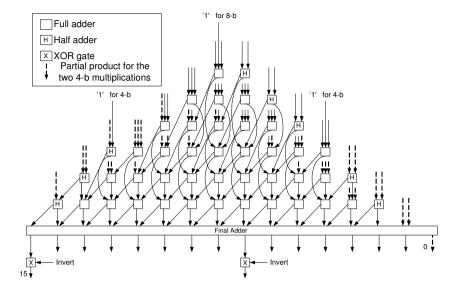

To allow for the full-precision multiplication of size N to coexist with two multiplications of size N/2 in the same multiplier, it is necessary to modify the partial-product generation and the reduction tree. For the N/2-bit multiplication in the MSP of the array all that is needed is to add a control signal that can be set to high, when the N/2-bit multiplication is to be computed and to low, when the full precision N multiplication is to be computed. To compute the N/2-bit multiplication in the LSP of the array, certain partial products need to be negated. This can easily be accomplished by changing the 2-input AND gate that generates the partial product to a 2-input NAND gate followed by an XOR gate. The second input of the XOR gate can then be used to invert the output of the NAND gate. When computing the N/2-bit LSP multiplication, the control input to the XOR gate is set to low making it work as a buffer. When computing a full-precision N multiplication the same signal is set to high making the XOR work as an inverter. Finally the MSB of the result needs to be negated and this can again be achieved by using an XOR gate together with an inverted version of the control signal for the XOR gates used in the partial-product generation.

Setting unwanted partial products to zero can be done by 3-input AND gates as for the unsigned case.

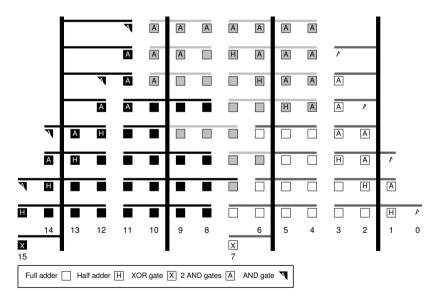

**Figure 1.9:** Block diagram of a signed 8-bit multiplication, using the Baugh-Wooley algorithm, where a 4-bit multiplication, shown in white, is computed in parallel with a second 4-bit multiplication, shown in black.

Fig. 1.9 shows an implementation of a twin-precision 8-bit BW multiplier. The modifications of the reduction tree compared to the unsigned 8-bit multiplier in Fig. 1.6 consist of three things; *i*) the half adders in column 4 and 8 have been changed to full adders in order to fit the extra sign bits that are needed, *ii*) for the sign bit of the 4-bit MSP multiplication there is no half adder that can be changed in column 12, so here an extra half adder has been added which makes it necessary to also add half adders for the following columns of higher precision, and *iii*) finally XOR gates have been added at the output of column 7 and 15 so that they can be inverted.

The simplicity of the BW implementation makes it easy to also compute unsigned multiplications. All that is needed is to set the control signals accordingly, such that none of the partial products are negated, the XOR gates are set to not negate the final result and all the sign bits are set to zero.

### 1.3 A Modified-Booth Implementation

Modified Booth (MB) is a popular algorithm and commonly used for implementation of signed multipliers. MB is a more complicated algorithm for signed multiplication than Baugh-Wooley (BW), but it has the advantage of only producing half the number of partial products. In this section a twin-precision multiplier based on the MB algorithm will be presented.

### 1.3.1 Algorithms for Modified Booth

The original-Booth algorithm [14] is a way of coding the partial products generated during a  $s=x\times y$  multiplication. This is done by considering two bits at a time of the x operand and coding them into  $\{-2,-1,0,1,2\}$ . The encoded number is then multiplied with the second operand, y, into a row of recoded partial products. The number of recoded partial products is fewer than for a scheme with unrecoded partial products and this can be translated into higher performance.

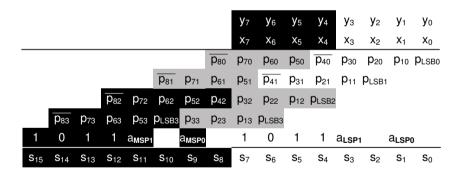

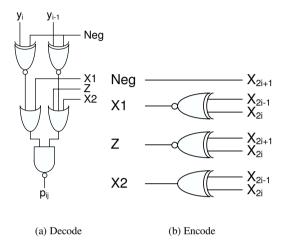

The drawback of the original-Booth algorithm is that the number of generated partial products depends on the x operand, which makes the Booth algorithm unsuitable for implementation in hardware. The MB algorithm [15] by MacSorley remedies this by looking at three bits at a time of operand x. Then we are guaranteed that only half the number of partial products will be generated, compared to a conventional partial product generation using 2-input AND gates. With a fixed number of partial products the MB algorithm is suitable for hardware implementation. Fig. 1.10 shows which parts of the x operand that are encoded and used to recode the y operand into a row of partial products.

Figure 1.10: 8-bit modified-Booth encoding.

A MB multiplier works internally with two's complement representation of the partial products, in order to be able to multiply the encoded  $\{-2, -1\}$ with the y operand. To avoid having to sign extend the rows of of recoded partial products, the sign-extension prevention scheme presented by Fadavi-Ardekani [16] has been used. In two's complement representation, a change of sign includes the insertion of a '1' at the Least Significant Bit (LSB) position. To avoid getting an irregular partial-product array we draw on the idea of Yeh et al. [17], called modified partial-product array. The idea is to pre-compute the impact on the two least significant positions of a row of recoded partial products by the insertion of a '1' during sign change. The pre-computation calculates the addition of the LSB with the potential '1', from which the sum is used as the new LSB for the row of recoded partial products. An potential carry from the pre-computation is inserted at the second least significant position. The pre-computation of the new LSB can be done according to Eq. 1.4. The pre-computation of a potential carry is as given by Eq. 1.5. Here Eq. 5.2 is different from that used by Yeh et al. [17].

$$p_{LSBi} = y_0(x_{2i-1} \oplus x_{2i}) \tag{1.4}$$

$$a_i = x_{2i+1}(\overline{x_{2i-1} + x_{2i}} + \overline{y_{LSB} + x_{2i}} + \overline{y_{LSB} + x_{2i-1}})$$

(1.5)

An illustration of an 8-bit MB multiplication with the sign-extension prevention and modified partial-product array scheme can be seen in Fig. 1.11.

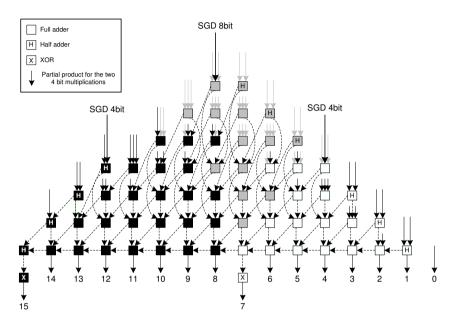

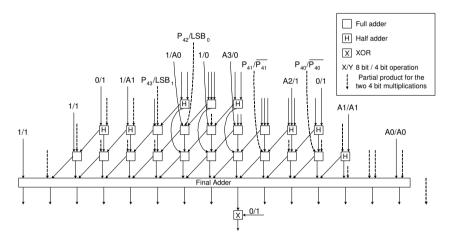

### 1.3.2 Twin-Precision Using the modified-Booth Algorithm

Implementing twin-precision together with the MB algorithm is not as straightforward as for the BW implementation (Section 1.2). It is not possible to take

**Figure 1.11:** Illustration of a signed 8-bit multiplication using the modified-Booth algorithm.

the partial products from the full-precision MB multiplication and use only the partial products that are of interest for the low-precision MB multiplications. The reason for this is that all partial products are not computed the same way and there exist several special cases that need to be handled.

**Figure 1.12:** *Illustration of a signed 8-bit multiplication using the modified-Booth algorithm.*

By comparing the two multiplications in Fig. 1.11 and Fig. 1.12 (for which we used N=8), we can see what needs to be handled in order to switch between the different modes of operation:

- The partial products that are denoted  $p_{40}$  and  $p_{41}$  during normal 8-bit multiplication (Fig. 1.11) need to define partial products that are used to prevent sign extension in the low-precision 4-bit multiplication in the LSP (Fig. 1.12).

- The partial-products that are denoted  $p_{42}$  and  $p_{43}$  during normal 8-bit multiplication need to define  $p_{LSB2}$  and  $p_{LSB3}$  for the low-precision 4-bit multiplication in the MSP.

- The a<sub>MSP0</sub> and a<sub>MSP1</sub> that are needed for the multiplication in the MSP have to be added.

- The pattern of 1's and 0's for the normal 8-bit multiplication cannot be used in low-precision mode. For the two 4-bit multiplications, we need two shorter patterns of 1's and 0's.

The implementation of the MB twin-precision multiplication does not call for any significant changes to the reduction tree of a conventional MB multiplier. When comparing the multiplications in Fig. 1.11 and Fig. 1.12, we can see that the position of the signals in the lowest row is the only difference that has an impact on the reduction tree. This means that there is a need for an extra input in two of the columns (N/2 and 3N/2) compared to the conventional MB multiplier; this requires two extra half adders in the reduction tree.

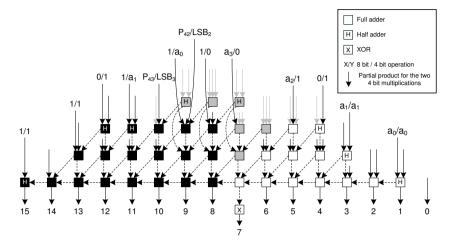

The biggest difference between a conventional MB multiplier and a twin-precision MB multiplier is the generation of inputs to the reduction tree. To switch between modes of operation, logic is added to the recoder to allow for generation of the partial products needed, for sign-extension prevention as well as  $p_{LSBi}$ , which are needed for N/2-bit multiplications in the LSP and the MSP, respectively. There is also a need for multiplexers that, depending on the mode of operation, select the appropriate signal as input to the reduction tree. Further, partial products that are not being used during the computation of N/2-bit multiplications have to be set to zero in order to not corrupt the computation. An example of an 8-bit MB twin-precision multiplier is shown in Fig. 1.13.

**Figure 1.13:** Block diagram of a signed 8-bit multiplication using the modified-Booth algorithm, where a 4-bit multiplication, shown in white, is computed in parallel with a second 4-bit multiplication, shown in black.

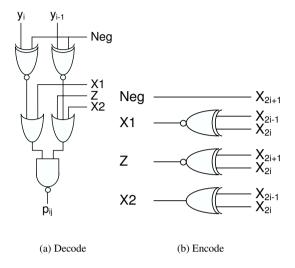

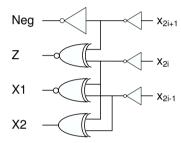

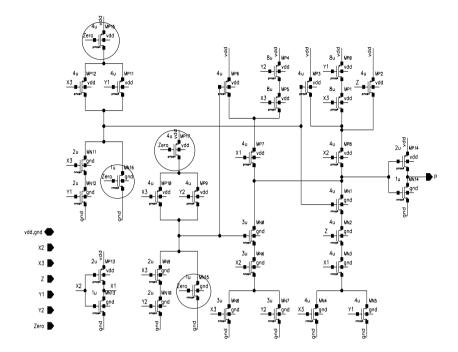

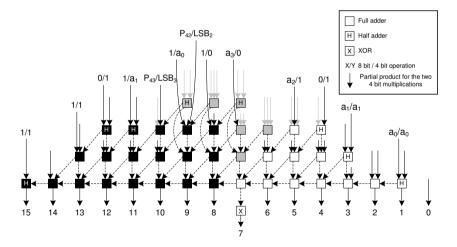

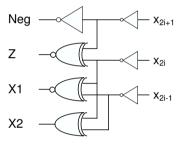

The logic encode and decode can be implemented in many different ways. For this implementation we have chosen the encoding scheme presented by Yeh *et al.* [17], since they claim that their recoding scheme is faster than competing schemes. The circuits for encoding and decoding is shown in Fig. 1.14.

For the partial products that need to be set to zero, an extra 2-input AND gate has been added at the output of the decode stage. The second input of the AND gate can then be used as a control signal, as in the case of for the unsigned and BW implementations. This is a straightforward method, and it is possible to construct even more efficient solutions for setting the partial product to zero. A decode circuit based on a custom layout, capable of setting the output to zero, can be found in PAPER III [18]. The outputs of the encoders have also been set to zero by using AND gates. This is not necessary for correct operation, but it reduces the power dissipation when computing N/2-bit multiplications due to reduced switching.

Figure 1.14: Encode and decode circuit for modified Booth.

For correct operation the input to the encoder for the first row in the N/2-bit MSP multiplication has to be set to zero, instead of using  $x_{N/2-1}$  as its input. An example of the encoding scheme for two 4-bit multiplications can be seen in Fig. 1.15.

Figure 1.15: Encoding scheme for two 4-bit multiplications.

In order to separate the two different N/2-bit multiplications, such that the multiplication in the LSP does not interfere with the multiplication in the MSP, we need to consider some other issues. By looking at the pattern of 1's and 0's that is used for sign-extension prevention, we see that the most significant '1' is only used to invert the final  $s_{2N-1}$ -bit. However, the carry that this extra '1'

potentially could generate is not of interest for the final result. If the most significant '1' for the multiplication in the LSP would be inserted into the reduction tree it would mean that a carry could be generated. This potential carry would propagate into the multiplication in the MSP and corrupt the result. To avoid inserting the most significant '1', an XOR gate is added after the final adder allowing the MSB of the N/2-bit LSP multiplication to be negated, which is the sole purpose of the most significant '1'.

# 1.4 Simulation Setups

To evaluate the efficiency of the twin-precision technique a multiplier generator has been written [19]. The generator is capable of generating VHDL descriptions of conventional Baugh-Wooley (BW) and modified-Booth (MB) multipliers as well as twin-precision versions of both of these, according to the schemes presented in the previous sections (1.2 and 1.3). A Kogge-Stone [20] adder was chosen as final adder for all types of multipliers. The VHDL generator has been verified to generate correct multipliers of sizes up to 16 bits by simulating all possible input patterns and verifying the result using Cadence NC-VHDL [21]. For multipliers larger than 16 bits, the functionality was verified by feeding the multipliers with a finite random input pattern and verifying the result.

The VHDL descriptions were synthesized using Design Compiler [22] by Synopsys together with a commercially available 0.13- $\mu$ m technology. For delay and power estimations, Synopsys PrimeTime [23] and PrimePower [24] were used. The delay has been estimated by assuming a 10 fF load on the primary output signals and a medium-size buffer from the cell library as driver for primary input signals. The chosen buffer cell is specified to be capable of driving approximately 150 minimum-size XOR gates. This is of course an overkill for the smaller multipliers of this evaluation but the same driver has been used for consistency of our analysis. For average power analysis, a clock period of 5 ns (200 MHz) and PrimePower's default values for switching activity. Further, it was assumed that the twin-precision multipliers will operate in the same mode (Full, 1xN/2, or 2xN/2 precision) for a long period of time. The power

for the control signals has not been included, since these low-activity signals would only have a minor contribution to the total power. All simulations were conducted with a supply voltage  $V_{dd}$  of 1.3 V and default temperatures for the respective tools.

The multipliers have not been taken through place and route, but as will be shown later in this section the area overhead of the twin-precision multipliers is not significant. Thus the total wire length of the multipliers is expected to be equal and so is the effect of cross talk.

#### 1.4.1 Synthesized Baugh-Wooley Netlist

The synthesis and the timing analyses showed that the simplicity of the BW implementation comes with an added benefit in that it does not create high fanout signals. The signals with highest fanout in the BW case are the input signals, which are connected to the input of N 2-input AND gates for a multiplier of size N. This creates a reasonable fanout of the input signals for multipliers up to at least 64 bits without losing any significant performance<sup>2</sup>. The mapping of the BW multiplier VHDL code to gate-level netlist during synthesis was only constrained in the way that half and full adders of the reduction tree was mapped to their respective minimum-size cells and the map effort in Design Compiler was set to high.

# 1.4.2 Synthesized Modified-Booth Netlist

The first attempt of synthesizing the VHDL code for the generated MB multipliers exposed a big problem with high fanout signals. This can easily be realized by investigating the encode and decode circuits from Fig. 1.14. As can be seen, the  $x_{2i+1}$  input signal goes straight through the encoder as the NEG signal and drives two XNOR gates for each partial product of a single row. This means that the fanout of half of the primary x-inputs is at least 2N XNOR gates for a multiplier of size N. Further, the encoder outputs X1, Z, and X2 drive N

<sup>&</sup>lt;sup>2</sup>This observation is based on medium-sized drivers for primary input signals.

decoders creating a need for large XOR and XNOR gates in the encode stage, which increases the fanout of the x-inputs even more.

To deal with the fanout problem, the X1, Z and X2 signals fanout have been reduced by instantiating multiple encoders for each row of partial products. To limit the fanout of the  $x_{2i+1}$  signal an inverter buffer has been inserted to drive the NEG signal. Finally min-size inverters have been added to  $x_{i-1}$ ,  $x_i$ , and  $x_{i+1}$ , inputs of the encoder, thus, the fanout of primary x-inputs is reduced. The new encode circuit can be viewed in Fig. 1.16.

Figure 1.16: Buffered encode circuit for fanout reduction.

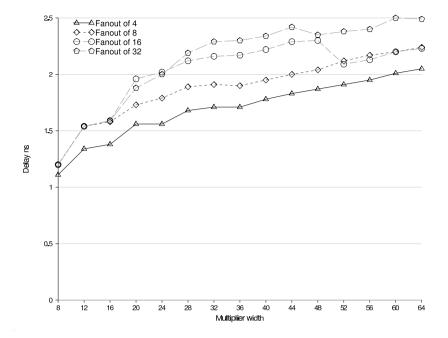

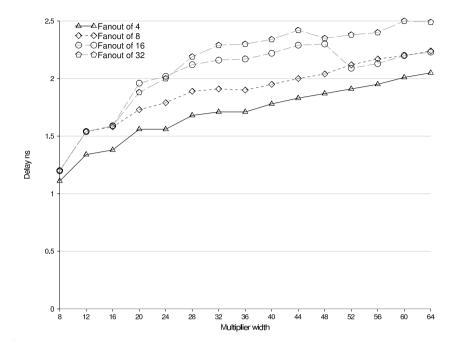

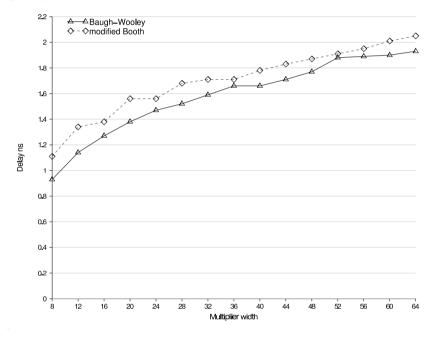

Fig. 1.17 presents a graph showing the effect on total delay when a maximum of 4, 8, 16, or 32 decoders have been connected to each of the new encoders of Fig. 1.16. The graph clearly shows the benefit in speed by reducing the fanout of the encoders, thus we have chosen to limit the maximum number of decoders connected to each encoder to four. The effect on power and area of the choice of fanout will be discussed later in this section.

The mapping of the MB multiplier VHDL code to gate-level netlist has been constrained in such way that Design Compiler could not remove the minimum-size inverters of the new encoder, Fig. 1.16. In all other respects the synthesized netlist of the MB multiplier has been constrained in the same way as the BW netlist. In other words half and full adders of the reduction tree have been mapped to their respective cells of minimum size from the cell library and the map effort was set to high.

Figure 1.17: Impact on the total delay for different fanout of the encoder.

#### 1.5 Results and Discussion

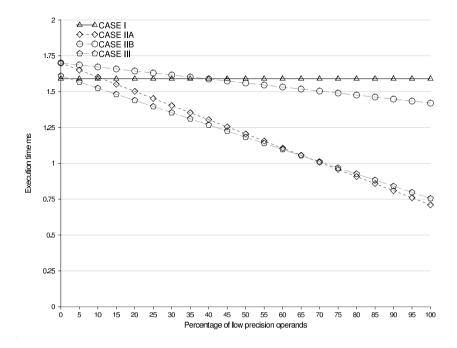

It is possible to operate the twin-precision multiplier in three different modes: *i*) the full-precision mode, denoted N, ii) the single N/2-bit mode, denoted 1xN/2, and iii) the double-throughput N/2-bit mode, denoted 2xN/2.

# 1.5.1 Power Dissipation

One of the reasons to use the twin-precision technique for executing low-precision multiplications is to reduce power dissipation of the multiplier<sup>3</sup>. Dynamic power is directly dependent on the switching activity ( $\alpha_i$ ) in each node. Eq. 1.6 gives the switching power given a switching voltage of  $V_{dd}$  and a load capacitance in each node of  $C_{Li}$  for a circuit operating with a frequency of  $f_{clk}$ .

<sup>&</sup>lt;sup>3</sup>The other reason is the possibility of executing two multiplications concurrently.

$$P_{switching} = \sum \alpha_i C_{Li} V_{dd}^2 f_{clk} \tag{1.6}$$

When operating a twin-precision multiplier in 1xN/2 or 2xN/2 mode large parts of the partial-product array are forced to zero. This in turn has the effect that the total switching activity is significantly reduced, since large parts of the logic are kept at a constant level. This has a dramatic effect on total power dissipation.

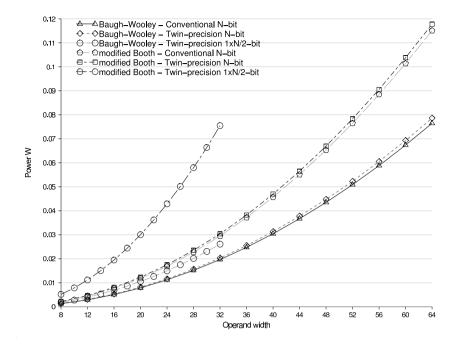

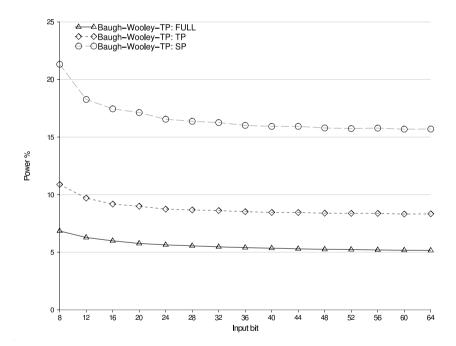

**Table 1.1:** Average power dissipation per operation for an N-bit multiplier operating at 200 MHz.

|                | Conventional Twin-pred |      | -precision | N-bit |

|----------------|------------------------|------|------------|-------|

|                | N-bit                  | N    | 1xN/2      | 2xN/2 |

| Baugh-Wooley   | 100%                   | 103% | 35%        | 32%   |

| Modified Booth | 151%                   | 153% | 98%        | 66%   |

As can be seen in Table 1.1, there is a significant reduction in power when operating an N-bit twin-precision multiplier in 1xN/2-bit or 2xN/2-bit mode. When operating in 2xN/2-bit mode, the total power dissipation is of course larger than for 1xN/2-bit mode, but since the two N/2-bit multiplications are computed concurrently the power dissipation per multiplication becomes lower. A twin-precision multiplier has a small overhead when operating in full N precision mode compared to a conventional multiplier. Table 1.1 also shows that a twin-precision implementation of modified Booth (MB) is not as efficient as a twin-precision implementation of Baugh-Wooley (BW). MB is clearly not suitable for low-power implementations.

**Table 1.2:** Average power dissipation per operation, comparing a conventional N/2-bit multiplier with an N-bit twin-precision multiplier when operating at 200 MHz.

|                | Conventional | Twin-precision N-bit |       |

|----------------|--------------|----------------------|-------|

|                | N/2-bit      | 1xN/2                | 2xN/2 |

| Baugh-Wooley   | 100%         | 136%                 | 128%  |

| Modified Booth | 151%         | 384%                 | 251%  |

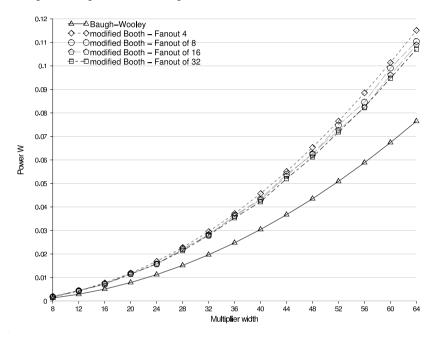

**Figure 1.18:** Total power in W for conventional Baugh-Wooley and modified Booth as well as twin-precision versions of both, when operating at 200 MHz. For the twin-precision implementations, the power for a single N/2 multiplication is also given.

Fig. 1.18 shows total power dissipation for both conventional BW and MB multipliers and their respective twin-precision implementations. As can be seen, when operating a twin-precision multiplier in 1xN/2 mode (as well as in 2xN/2 mode, which is not shown in the graph) the power dissipation is slightly higher than for a conventional multiplier that is of size N/2. Table 1.2 shows the average difference in power dissipation.

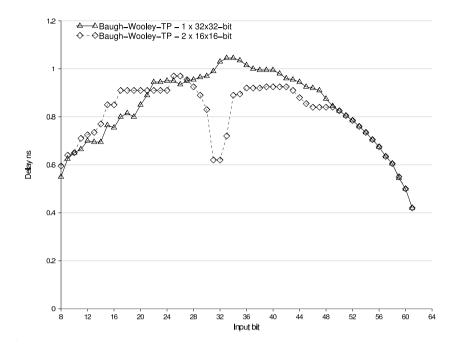

# 1.5.2 **Delay**

The twin-precision technique was conceived with a minimum delay overhead in mind for the N-bit multiplication. This is the main reason as to why the struc-

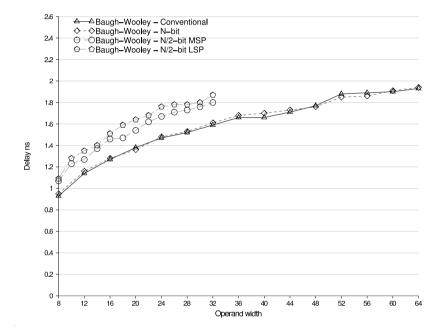

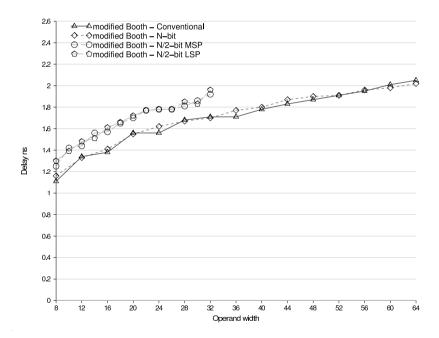

ture of the reduction tree has been modified as little as possible. This strategy has proven to be very efficient, the delay overhead for both the BW (Fig. 1.19) and the MB (Fig. 1.20) implementation is less than 1%, (on average 0.7% and 0.6%, respectively). This comes at the cost of a higher delay overhead for the N/2-bit multiplication compared to a conventional multiplier of size N/2, since the reduction tree and the final adder are not primarily optimized for these precisions.

**Figure 1.19:** *Total delay in ns for a conventional Baugh-Wooley implementation and its twin-precision counterpart.*

As can be seen from Table 1.3 there is a delay overhead for N/2-bit multiplication within the twin-precision multiplier when compared to a conventional fixed-size N/2-bit multiplier. However, the twin-precision's N/2-bit is still 5-10% faster than the full-precision multiplier for the BW implementation and about 6% faster for the MB implementation. The shorter delay of the N/2-bit

| N-bit twi | n-precision multiplier | :            |           |                |

|-----------|------------------------|--------------|-----------|----------------|

|           |                        | Conventional | Twin-prec | ision $N$ -bit |

|           | į                      | M /O 1.4     | I CD M/O  | MCD M/O        |

**Table 1.3:** Average delay when comparing a conventional N/2-bit multiplier with an

|                | Conventional      | Twin-precision N-bi |         |

|----------------|-------------------|---------------------|---------|

|                | N/2-bit LSP $N/2$ |                     | MSP N/2 |

| Baugh-Wooley   | 100%              | 118%                | 115%    |

| Modified Booth | 108%              | 122%                | 122%    |

multiplications can be used for either clocking the multiplier faster, thus increasing the throughput or reducing the supply voltage to further reduce power dissipation. As can be seen from Eq. 1.6, power is quadratically dependent on the supply voltage  $(V_{dd})$ . The gain in power reduction from reducing the supply voltage in the presence of delay margins has not been investigated.

**Figure 1.20:** Total delay in ns for a conventional modified-Booth implementation and its twin-precision counterpart.

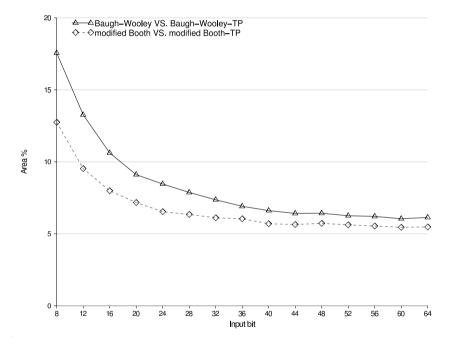

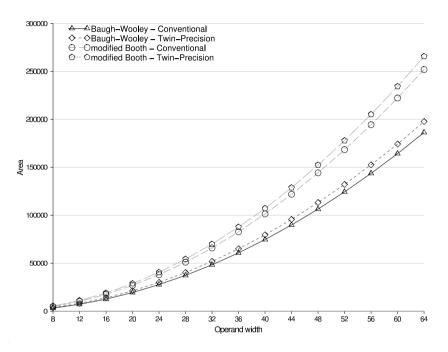

#### 1.5.3 Area